Gedruckte Schaltungen (PCBs) sind das Rückgrat moderner elektronischer Geräte, wobei sich die Fortschritte bei der Herstellung direkt auf die Leistung und Zuverlässigkeit der Produkte auswirken. Mit der rasanten Entwicklung von 5G, IoT, KI und anderen Spitzentechnologien erlebt die Leiterplattenindustrie eine beispiellose Innovation. Dieser Artikel bietet eine eingehende Analyse der wichtigsten Leiterplattenherstellungstechnologien, ihrer Anwendungen und Zukunftstrends und vermittelt so ein umfassendes Verständnis dieses Fachgebiets.

Inhaltsübersicht

Überblick über die PCB-Herstellungsprozesse

PCB manufacturing has evolved from simple single-layer boards to today’s high-density interconnect (HDI) multilayer boards, continuously pushing the limits of physical design. The three primary PCB manufacturing processes are:

Subtraktives Verfahren: Die traditionellste Methode, bei der ein Fotolack auf ein kupferbeschichtetes Laminat aufgetragen, belichtet wird, um ein Schaltungsmuster zu erzeugen, und dann geätzt wird, um ungeschütztes Kupfer zu entfernen. Dieses Verfahren ist zwar ausgereift, hat aber eine begrenzte Präzision und wird den modernen HDI-Anforderungen nur schwer gerecht.

Vollständig additiver Prozess (SAP): Verwendet ein isolierendes Substrat mit einem lichtempfindlichen Katalysator. Nach selektiver Belichtung wird Kupfer nur dort chemisch abgeschieden, wo es zur Bildung von Schaltkreisen benötigt wird. Dies ermöglicht eine hohe Präzision, erfordert jedoch eine strenge Material- und Prozesskontrolle.

Modifiziertes Semi-Additiv-Verfahren (mSAP): Kombiniert die Vorteile des subtraktiven und des additiven Verfahrens. Eine dünne Keimschicht aus Kupfer wird chemisch abgeschieden, selektiv galvanisch abgeschieden, um die Leiterbahnen zu verdicken, und dann wird das überschüssige Kupfer weggeätzt. Dieses Verfahren ist ideal für ultrafeine Schaltungen und hat sich zu einer Standardtechnologie für hochwertige Leiterplatten entwickelt.

Zentrale fortschrittliche PCB-Fertigungstechnologien

Via-in-Pad: Ermöglichung von High-Density-Verbindungen

Bei der Via-in-Pad-Technologie werden leitende Durchkontaktierungen direkt in den Bauteilpads platziert, wodurch sich die Platzausnutzung auf der Leiterplatte erheblich verbessert.

Die wichtigsten Vorteile:

- Spart über 30% Platz auf der Platine, ideal für kompakte Designs

- Verkürzt die Signalwege und verbessert die Leistung von Hochgeschwindigkeitsschaltungen

- Bietet zusätzliche Wärmewege und verbessert die Wärmeableitung für Hochleistungskomponenten

Herausforderungen bei der Herstellung:

- Microvia Bohren: Requires laser drilling for 50–100 μm microvias with ±15 μm positioning accuracy

- Über das Füllen: Die vakuumunterstützte Harzfüllung sorgt für blasenfreie Hohlräume, wobei die Materialschrumpfung unter 2 % liegt.

- Planarität der Oberfläche: Post-filling, precision grinding ensures surface flatness within 5 μm for reliable soldering

- Thermisches Stressmanagement: Filler materials must match copper’s thermal expansion coefficient to prevent cracking

Anwendungen:

- Smartphone-Motherboards (insbesondere für Prozessoren und Speicher)

- High-End-GPUs und Server-Motherboards

- Miniaturisierte IoT-Geräte

- LED-Arrays mit hoher Dichte

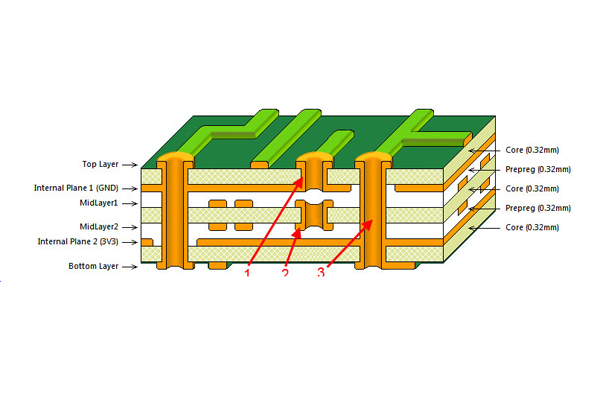

Blind und Buried Vias: 3D-Verbindungslösungen

Blind- und vergrabene Durchkontaktierungen ermöglichen selektive Lagenverbindungen und damit ein dreidimensionales PCB-Routing.

Technologie-Vergleich:

| Typ | Struktur | Herstellungsverfahren | Hauptnutzen |

|---|---|---|---|

| Blind Via | Verbindet äußere mit inneren Schichten | Laser-/gesteuertes Tiefenbohren | Verringert die Auswirkungen von Signalabrissen |

| Begraben über | Vollständig innerhalb der inneren Schichten | Laminiert nach der Schichtverarbeitung | Freisetzung von Routing-Raum auf der äußeren Schicht |

Zentrale Prozessherausforderungen:

- Tiefenkontrolle: Laser drilling requires precise energy/pulse control (±10 μm tolerance)

- Ebenenausrichtung: High-precision registration systems ensure ≤25 μm misalignment

- Gleichmäßigkeit der Beschichtung: Pulse plating ensures even copper deposition (≥18 μm in vias)

- Zuverlässigkeitsprüfung: Thermal cycling (-55°C to 125°C, 1000 cycles) and impedance testing

Anwendungen in der Industrie:

- 4G/5G-Basisstation RF-Module

- Luft- und Raumfahrt und Verteidigungselektronik

- Schalttafeln für medizinische Geräte

- Sensormodule für autonome Fahrzeuge

Modifiziertes Semi-Additiv-Verfahren (mSAP): Ultrafeine Schaltungsfertigung

mSAP uses a “thin seed layer + selective plating” approach to achieve sub-30 μm trace/space, surpassing traditional etching limits.

Prozessablauf:

- Vorbereitung des Substrats: Low-roughness base material (Rz < 1.5 μm)

- Ablagerung der Keimschicht: 0.3–1 μm thin copper via electroless plating

- Musterung: Laser Direct Imaging (LDI) with 5 μm resolution

- Beschichtung: Acid copper electroplating (±2 μm thickness control)

- Entfernung der Saatschicht: Micro-etching with <3 μm undercut

Metriken zur Qualitätskontrolle:

- Gleichmäßigkeit der Leiterbahnbreite: CV < 5% über die gesamte Platte

- Kupferdickenschwankungen: <10% innerhalb der Platte

- Surface defects: <3 defects per m²

Typische Produkte:

- Substratähnliche Leiterplatten für Smartphones (SLP)

- Substrate für das Wafer-Level-Packaging

- Millimeterwellen-Antennen-Arrays

- Verbindungsmodule mit ultrahoher Dichte

Industrielle Anwendungen fortschrittlicher PCB-Technologien

Unterhaltungselektronik

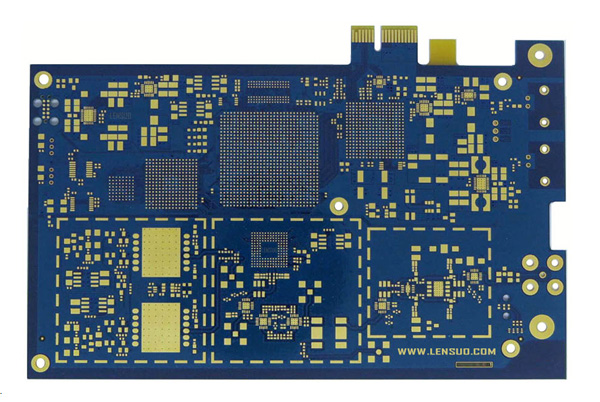

Smartphones and tablets drive advanced PCB adoption. Flagship smartphone motherboards use any-layer HDI and mSAP to achieve 20/20 μm trace/space rules, packing 14+ layers into 80×120 mm areas. Wearables employ rigid-flex PCBs, maintaining reliability at <3 mm bend radii.

Telekommunikationsinfrastruktur

5G-Basisbandgeräte erfordern Hochfrequenz-Leiterplatten mit:

- Dielectric constant (Dk): 3.0±0.05 @ 10 GHz

- Verlusttangens (Df): <0,002 @ 10 GHz

- Phase consistency: ±1.5°/inch

Diese erfordern spezielle Harzsysteme und kontrollierte Impedanzverfahren.

Kfz-Elektronik

Autonome Systeme bringen neue Anforderungen mit sich:

- Radar PCBs: Ra < 0.3 μm surface roughness for 77 GHz

- Batterie-Management: 6-lagige, 2 oz schwere Kupferplatten (Durchkontaktierungen im Verhältnis 8:1)

- Anzeigen:Ultradünne flexible Schaltungen (>100k Biegezyklen)

Industrie & Medizinische Ausrüstung

Industrielle Steuerungen erfordern:

- 10+ Lagen Power PCBs

- -40°C to 150°C operating range

- Vibration resistance (5–500 Hz, 5 Grms)

Die medizinische Bildgebung beruht auf:

- Rauscharmes Schaltungsdesign

- Hochdichtes analoges Routing

- EMI-Abschirmungsstrukturen

Zukünftige Trends & Technische Herausforderungen

Werkstoff-Innovationen

Hochfrequenz-Materialien:

- Modifizierte PTFE-Verbundwerkstoffe

- Flüssigkristallpolymer (LCP)-Folien

- Nano-poröses Siliziumdioxid

Thermisches Management:

- >5 W/mK Wärmeleitfähigkeit Harze

- Mit Graphen verstärkte Substrate

- Isolierte Metallsubstrate

Prozess-Durchbrüche

Heterogene Integration:

- Embedded passives (>100/cm²)

- Chip-on-Board-Technologie (COB)

- Optoelektronische Hybridschaltungen

Präzisionsfertigung:

- Pikosekunden-/Femtosekunden-Laserbohren

- Metallisierung durch Atomlagenabscheidung (ALD)

- Nanoimprint-Lithographie

Initiativen zur Nachhaltigkeit

Umweltverträgliche Prozesse:

- Cyanidfreie Vergoldung

- Stromloses Kupfer mit niedrigem COD-Wert

- Lötmasken auf Wasserbasis

Kreislaufwirtschaft:

- >99,5% Kupferrückgewinnung

- Energiearme Fertigung

- Biologisch abbaubare Substrate

FAQ: Fortschrittliche PCB-Herstellung

Q1: Wie verbessert das Via-in-Pad die thermische Leistung?

A1: Copper-filled vias create thermal pathways, reducing thermal resistance by >40% in 3×3 via arrays. Optimal fill density is 60–70% for thermo-mechanical reliability.

F2: Was sind die Vorteile der Signalintegrität von Blind-/Buried-Vias?

A2: Im Vergleich zu Durchgangslöchern sind sie:

- Shorten signal paths by 30–50%

- Reduce crosstalk by 6–8 dB @ 10 GHz

- Verbesserung der Impedanzanpassung (15% geringere Reflexion)

- Cut delay by 20–30 ps/inch

F3: Wie übertrifft MSAP die traditionellen subtraktiven Verfahren?

A3: Die wichtigsten Vorteile sind:

- Trace width accuracy: ±2 μm vs ±8 μm

- Near-vertical sidewalls (85–90° vs 45–60°)

- Finer geometries (15/15 μm vs 50/50 μm)

- Tighter impedance control (±5% vs ±10%)

Q4: How to evaluate a manufacturer’s blind/buried via capability?

A4: Bewerten:

- Technical specs (≤50 μm microvias, ±25 μm registration)

- Zuverlässigkeitsdaten (Temperaturwechsel, Querschnittsanalyse)

- Inspektionsmethoden (3D-Röntgen, AOI-Abdeckung)

- Produktionsstabilität (>90% Ausbeute im Maßstab)

Q5: What breakthroughs will shape PCB tech in 3–5 years?

A5: Wichtige Entwicklungen:

- Höhere Dichte: 10/10 μm traces, hybrid mSAP/SAP

- Heterogene Integration: Eingebettete Aktive/Passive, optische Verbindungen

- Fortschrittliche Materialien: mmWave verlustarme Dielektrika (Dk<2,5, Df<0,001)

- Intelligente Fertigung: KI-gesteuerte Optimierung, digitale Zwillinge

- Nachhaltigkeit: >95% Materialrecycling, 30% Energiereduktion

Da die Elektronik immer leistungsfähiger, miniaturisierter und effizienter wird, stößt die Leiterplattentechnologie immer wieder an physikalische Grenzen.Das Verständnis dieser Innovationen ermöglicht es Designern und Beschaffungsspezialisten, fundierte Entscheidungen zu treffen und die Produktentwicklung der nächsten Generation voranzutreiben.

Mehr dazu lesen

1.PCB-Herstellung Proofing-Prozess

2.PCB Durchkontaktierungen

3.Verfahren zur Herstellung von Hochfrequenz-Leiterplatten