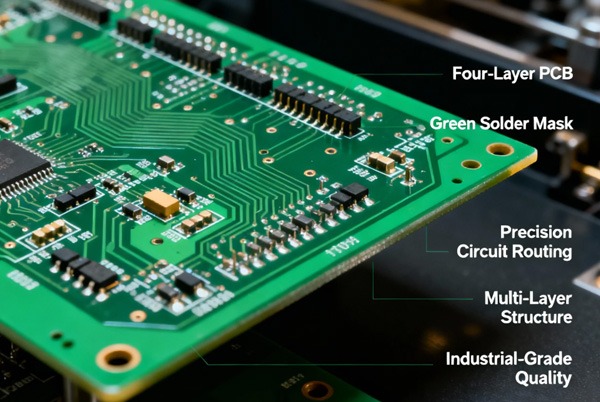

In der Unterhaltungselektronik, bei industriellen Steuerungsgeräten und in digitalen Hochgeschwindigkeitssystemen werden vierlagige Leiterplatten aufgrund ihrer überlegenen elektromagnetischen Verträglichkeit (EMV), Stromintegrität und Signalintegrität bevorzugt eingesetzt.

Inhaltsübersicht

4-Lagen PCB Stapelstruktur

Das Stackup-Design ist die Grundlage für die Leistung einer 4-lagigen Leiterplatte. Ein ungeeignetes Stackup kann zu Signalübersprechen, Stromversorgungsrauschen und EMI-Nichtkonformität führen.

1. Vergleich klassischer Stapelungsschemata

- Schema 1 (empfohlen)

- Oberste Schicht: Signalschicht

- Schicht 2: Massefläche (GND)

- Schicht 3: Stromversorgungsebene (PWR)

- Unterste Schicht: Signalschicht

- Vorteile: Die Grundplatte bietet eine solide Referenz für Signale der obersten Schicht. Die angrenzenden Strom- und Grundplatten bilden eine inhärente Entkopplungskapazität.

- Schema 2

- Oberste Schicht: Signalschicht

- Schicht 2: Stromversorgungsebene

- Schicht 3: Grundplatte

- Unterste Schicht: Signalschicht

- Anwendbare Szenarien: Hochstromgeräte (z. B. Motortreiber). Beachten Sie mögliche Änderungen der Referenzebene für Signale der unteren Schicht.

- Schema 3 (Mit Vorsicht verwenden)

- Oberste Schicht: Massefläche

- Schicht 2: Signalschicht

- Schicht 3: Signalschicht

- Unterste Schicht: Leistungsebene

- Risiken: Unvollständige Massefläche, lange Signalrückwege. Vor allem für niederfrequente, steckverbinderdominierte Leiterplatten geeignet.

2. Einstellungen der wichtigsten Parameter

- Dielektrische Dicke: Recommended 0.1–0.2mm between signal and reference planes to enhance inter-layer coupling.

- Kupfergewicht: Outer layers 1oz (35μm), inner layers 0.5oz (17.5μm). Can increase to 2oz for high-current areas.

- Rückzugskonstruktion: Power planes should be indented 40–80mil relative to the ground plane (20H rule) to reduce edge radiation.

Über Design

Vias sind für Verbindungen zwischen Schichten von entscheidender Bedeutung, führen jedoch zu parasitären Parametern, die Hochgeschwindigkeitssignale beeinträchtigen.

1. Über die Typenauswahl

- Durchkontaktierungen: Kostengünstig, geeignet für Standard-Signale und Stromanschlüsse.

- Blinde/vergrabene Durchkontaktierungen: Wird für das Escape-Routing von BGAs mit hoher Dichte verwendet, erhöht jedoch die Prozesskosten.

2. Berechnung parasitärer Parameter

- Parasitäre Kapazität:

C ≈ 1.41ε · T · D1 / (D2 - D1)

WoTist die Plattenstärke,D1ist der Bohrerdurchmesser,D2ist der Durchmesser der Unterlage. - Parasitäre Induktivität:

L ≈ 5.08h [ln(4h / d) + 1]

Wohist über die Länge,dist der Bohrerdurchmesser.

3. Über Nutzungsrichtlinien

- Power-Vias: Verwenden Sie größere Durchkontaktierungen (z. B. 12 mil Durchmesser/16 mil Bohrung) und platzieren Sie mehrere parallel, um die Impedanz zu reduzieren.

- Signal-Durchkontaktierungen: Bevorzugen Sie kleinere Durchkontaktierungen (z. B. 8 mil Durchmesser/12 mil Bohrung). Vermeiden Sie asymmetrische Platzierungen in Differentialpaaren.

- Thermische Durchkontaktierungen: Unter wärmeerzeugende Komponenten legen (z. B. 0,3-mm-Bohrer, 1,5-mm-Raster).

PCB-Routing

1. Routing-Verfahren

- Zuerst schwierige Bereiche angehen: Beginnen Sie mit dem Routing in komplexen Bereichen wie BGAs und Hochgeschwindigkeitsschnittstellen.

- Modulares Handling: Routen nach Funktionsblöcken (z. B. MCU, Speicher, analoge Schaltungen), um gegenseitige Störungen zu vermeiden.

- Aufräumrouting: Leiten Sie Signale mit niedriger Geschwindigkeit zuletzt weiter und optimieren Sie die Kanalauslastung durch Anpassen der Leiterbahnbreite und des Abstands.

2. Kritische Routing-Regeln

- Impedanzregelung:

- Single-ended: 50Ω. Differential pairs: 100Ω.

- Erreichen Sie dies durch Anpassen der Leiterbahnbreite, der Dielektrizitätskonstante und der Permittivität.

- Hochgeschwindigkeits-Signalverarbeitung:

- Priorisieren Sie die Verlegung von Taktsignalen auf inneren Schichten, bezogen auf eine Massefläche.

- Maintain length matching in differential pairs (≤5mil tolerance).

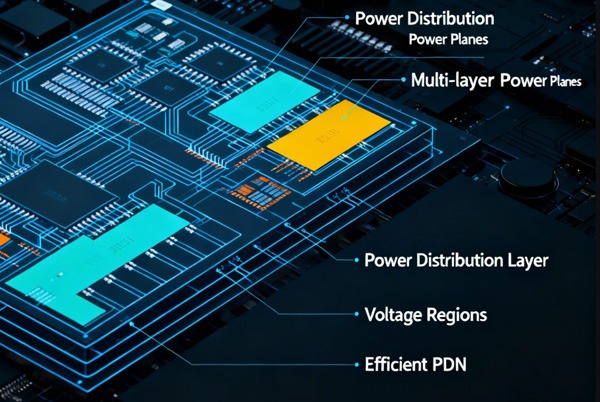

- Leistungsflächen-Segmentierung:

- Segmentieren Sie eine einzelne Stromversorgungsebene in maximal 3 Bereiche (z. B. 3,3 V, 5 V, 12 V).

- Use segmentation lines ≥0.5mm wide to prevent creepage issues.

Power Integrity Design

1. Platzierung des Entkopplungskondensators

- Auswahl: 0.1μF ceramic capacitors (high-frequency) + 10μF tantalum capacitors (low-frequency).

- Platzierung: Position close to IC power pins (≤3mm). Connect directly to power/ground planes via vias.

2. Integrität der Grundplatte

- Vermeiden Sie eine Aufteilung der Massefläche durch Signalleitungen, um niederohmige Rückwege zu gewährleisten.

- Connect digital and analog grounds at a single point using a ferrite bead or 0Ω resistor.

Designüberprüfung und Produktionsvorbereitung

1. DRC-Checkliste

- Trace Width/Spacing: General signals ≥6/6mil, Power traces ≥12/12mil.

- Drill-to-Copper Distance: ≥8mil to prevent short circuits.

2. Signalintegritätssimulation

- Verwenden Sie Tools wie HyperLynx oder Sigrity, um Anstiegszeit, Klingeln und Impedanzkontinuität zu überprüfen.

- Konzentrieren Sie sich auf die Überprüfung von Uhren, Differenzsignalen und Netzteilwelligkeit.

3. Ausgabe der Produktionsdatei

- Stellen Sie Gerber-Dateien (einschließlich Ebenen, Lötmaske, Bohrung), Impedanztestcoupons und Montagezeichnungen bereit.

Wichtige Erkenntnisse zum Design

- Bevorzugtes Stapelschema 1, wodurch eine Grundplatte neben den primären Signalschichten gewährleistet wird.

- Kosten und Leistung durch Design ausgleichen, unter Verwendung paralleler Stromdurchführungen zur Verringerung der Impedanz.

- Route nach dem Prinzip „Difficult First“, wobei Hochgeschwindigkeitssignale auf den inneren Schichten priorisiert werden.

- Begrenzen Sie die Stromsegmentierung auf 3 Regionen., Entkopplungskondensatoren in der Nähe von ICs platzieren.

- Mit DRC und Simulation validieren um Nacharbeiten in der Postproduktion zu vermeiden.