Eine vierlagige PCB-Leiterplatte ist eine mehrlagige Leiterplatte, die in der Regel aus einer inneren Signallage, einer inneren Stromversorgungslage, einer äußeren Signallage und einer äußeren Bauteilmontagelage besteht. Im Vergleich zu einseitigen und doppelseitigen Leiterplatten bieten vierlagige Leiterplatten eine höhere Integration, eine geringere Größe und eine stabilere Leistung, da die innere Versorgungslage (eine Lage, die auf gewöhnlichen Leiterplatten nicht zu finden ist) Strom weiterleiten kann, wodurch Störungen und Rauschen reduziert und die Stabilität der Schaltung gewährleistet wird.

Inhaltsübersicht

Technische Spezifikationen von 4-Lagen PCB-Platten

Grundlegende Struktur

Eine 4-Lagen-Leiterplatte nimmt die klassische Signal-Strom-Masse-Signal-Konfiguration an:

- Oberste Schicht: Bauteilmontage und Oberflächenverlegung

- Innere Schicht 1: Signalübertragungsschicht (Priorität für Hochfrequenzsignale)

- Innere Schicht 2: Leistungsebene (Power Plane)

- Unterste Schicht: Signalschicht und Lötfläche

Kernvorteile im Vergleich

| Leistungsmetrik | Doppellagige PCB | 4-Lagen PCB | Verbesserung |

|---|---|---|---|

| Routing-Dichte | 2-4 Linien/cm | 8-12 Linien/cm | 300% |

| Signalintegrität | 60-80Ω impedance variation | ±5% impedance control | 5x besser |

| Leistungsrauschen | 50-100mV | <10mV | 90%ige Reduzierung |

| EMC-Leistung | Erfordert zusätzliche Abschirmung | Eingebaute Abschirmungsschichten | Entspricht der Klasse B |

Typische Anwendungen

- Digitale Hochgeschwindigkeitsschaltungen

- Merkmale: Taktfrequenzen über 100MHz

- Umsetzung:Vollständige Rückführung über innere Masseflächen

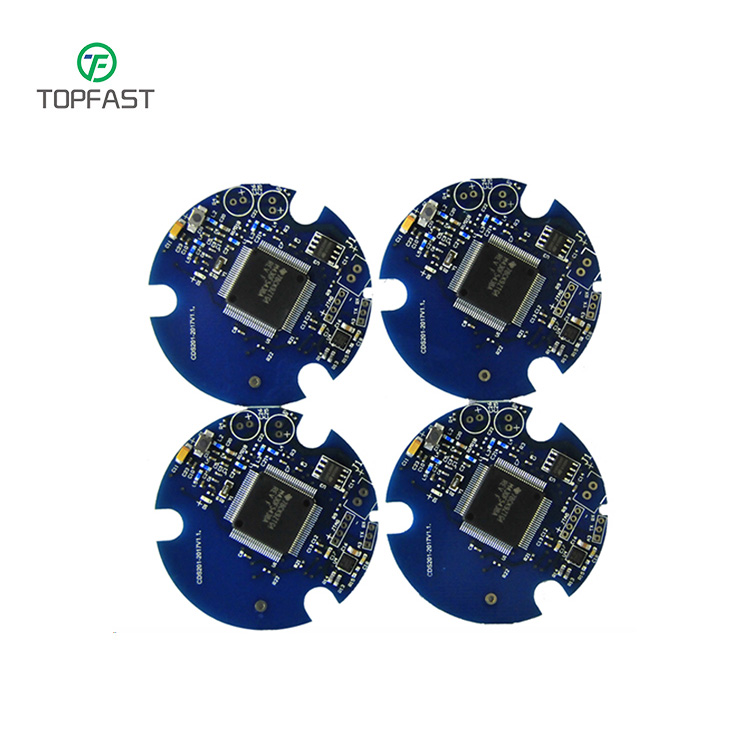

- Beispiel:ARM-Prozessorplatinen (6-Lagen-HDI mit Blind-/Buried Vias)

- Analog-gemischte Systeme

- Lösung: Getrennte digitale/analoge Stromversorgungen

- Aufbau:Analoge Signale auf der obersten Ebene + digitale Signale auf den inneren Ebenen

- Leistung:Crosstalk < -60dB @1GHz

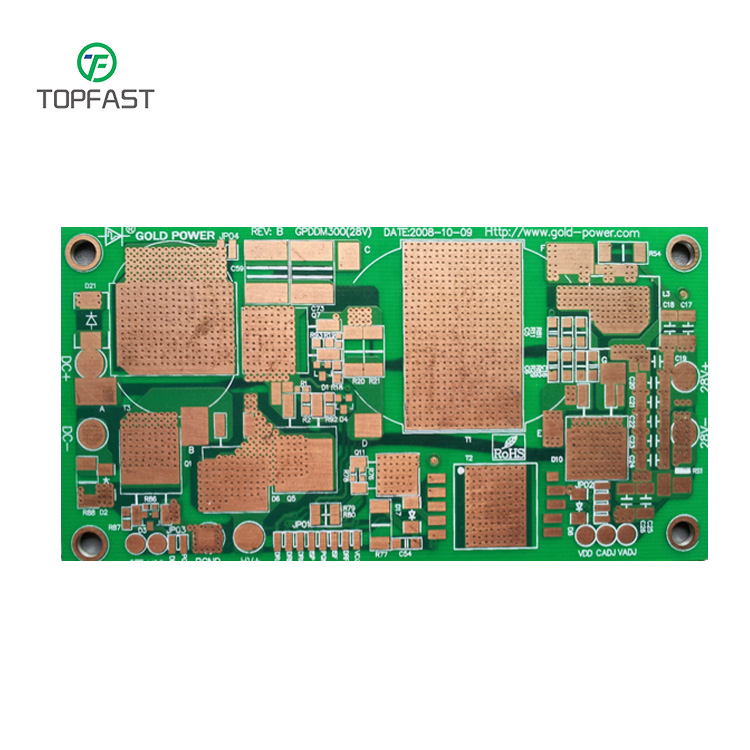

- Leistungselektronik-Design

- Konfiguration: Leistungsebene aus 2 Unzen dickem Kupfer

- Capability: Current density up to 10A/mm²

- Wärmemanagement: Via-Arrays zur Wärmeableitung

Schlüsselpunkte der Produktion

- Kontrolle der Laminierung

- Dielectric thickness: 0.2mm ±5%

- Kupfergewicht Optionen: 1 Unze / 2 Unzen

- Alignment accuracy: ≤50μm

- Über Design

- Durchgangsbohrung: 0,3mm/0,6mm (Lochdurchmesser/Pad)

- Blinde Durchkontaktierungen: L1-L2 oder L3-L4

- Vergrabene Durchkontaktierungen:L2-L3 (erfordert Laserbohren)

- Impedanzkontrolle

- Microstrip: 50Ω ±10% (outer layers)

- Stripline: 100Ω differential (inner layers)

- Verifizierung:TDR-Prüfung (Time Domain Reflectometry)

Leitlinien für die Auswahl

- Empfohlene Anwendungsfälle

- Operating frequency ≥50MHz

- Component count ≥100

- BGA packages (pitch ≤0.8mm)

- Erfordert 4+ Power-Domains

- Optimierung der Kosten

- Standard FR4 material (TG≥130℃)

- Mindestspur/Zwischenraum: 4mil/4mil

- Vermeiden Sie blinde/vergrabene Durchkontaktierungen

Hinweis: Moderne 4-Lagen-Leiterplatten unterstützen 3mil Leiterbahnen/Zwischenraum mit 0,25mm Microvias, wodurch eine mit 6-Lagen-Leiterplatten vergleichbare Leiterbahndichte erreicht wird. Gemäß den IPC-2221B-Normen können 4-Lagen-Leiterplatten eine Lebensdauer von 10 Jahren erreichen (Anwendungen in Industriequalität).

Umfassender Herstellungsprozess von 4-Lagen-PCB-Platten

Entwurfsplanungsphase

- EDA-Design-Verifizierung

- Professionelle Werkzeuge: Cadence Allegro/Mentor Xpedition

- Analyse der Signalintegrität (HyperLynx)

- Ausgabe: Produktionsdateien im Gerber 274X-Format

- Wichtige Parameter:

✓ Minimum trace/space: 3/3mil

✓ Impedance control: ±10%

✓ Via count: ≥2000/m²

Materialvorbereitung & Verarbeitung

- Auswahl kupferbeschichteter Laminate

- Standard FR-4 (TG150)

- Optionen für die Kupferstärke: 1/2oz einstellbar

- Dimensional tolerance: ±0.1mm

- Präzisionsbohren

- Ausstattung:6-achsige CNC-Bohrmaschine

- Genauigkeit:

✓ Hole position deviation: ≤25μm

✓ Hole diameter tolerance: ±50μm - Typische Parameter:

✓ Spindle speed: 150krpm

✓ Panel stack thickness: ≤2.4mm

Mehrschichtiges Laminierungsverfahren

- Ebenen-Stapelung

| Ebene | Bezeichnung | Dicke (mm) | Kupfer Gewicht | Primäre Funktion |

|---|---|---|---|---|

| Top | Signalschicht (L1) | 0.035 ±0.005 | 1 Unze | Platzierung von Bauteilen & Routing |

| Inneres | Leistungsebene (L2) | 0.50 ±0.05 | 2 Unzen | Stromverteilung & Entkopplung |

| Inneres | Bodenebene (L3) | 0.50 ±0.05 | 2 Unzen | Signalrückweg & EMI-Abschirmung |

| Unten | Signalschicht (L4) | 0.035 ±0.005 | 1 Unze | Sekundäres Routing & Löten |

2. Parameter für die Laminierung

- Temperature: 180±5℃

- Pressure: 300±50psi

- Duration: 90±10 minutes

- Vacuum level: ≤10mbar

Technologie der Musterübertragung

- LDI-Belastung

- Resolution: 20μm

- Alignment accuracy: ±15μm

- Kapazität: 50 Paneele/Stunde

- Ätzen von Schaltkreisen

- Etch factor: ≥3:1

- Undercut control: ≤10%

- Copper thickness uniformity: ±5%

Beschichtung & Oberflächenveredelung

- Metallisierung von Löchern

- Electroless copper: 0.5-1μm

- Electroplated copper: 25±5μm

- Hole wall pull strength: ≥1.0N/mm

2. Optionen für die Oberflächenausführung

| Oberfläche | Technische Spezifikation | Dickenbereich | Wesentliche Merkmale | Empfohlene Anwendungen | Haltbarkeitsdauer | IPC-Norm |

|---|---|---|---|---|---|---|

| ENIG (Chemisch Nickel Chemisch Gold) | Ni: 3-5μm Au: 0.05-0.1μm | Ni: 120-200μin Au: 2-4μin | – Ausgezeichnete Ebenheit – Gute Lötbarkeit – Aluminiumdraht verbindbar | – BGA-Gehäuse – Komponenten mit feinem Raster (<0,5mm) – Steckverbinder | 12 Monate | IPC-4552 |

| OSP (Organisches Konservierungsmittel für die Lötbarkeit) | 0.2-0.5μm | 8-20μin | – Kostengünstig – Bleifrei kompatibel – Einfaches Verfahren | – Unterhaltungselektronik – Allgemein SMT-Bestückung – Hochvolumige Produktion | 6 Monate | IPC-4555 |

| Immersionsdose | 0.8-1.2μm | 30-50μin | – Ausgezeichnete Lötbarkeit – Flache Oberfläche – Zum Einpressen geeignet | – Kfz-Elektronik – Hochzuverlässige Anwendungen – RF/Mikrowellen-Schaltungen | 9 Monate | IPC-4554 |

System zur Überprüfung der Qualität

- Elektrische Prüfung

- Test mit der fliegenden Sonde:

✓ Test speed: 200 points/sec

✓ Minimum pitch: 4 mil - Impedanztest:

✓ TDR resolution: 5ps

✓ Test points: ≥5/impedance line

- Visuelle Inspektion

- AOI:

✓ Resolution: 10μm

✓ Defect detection rate: ≥99.7% - Analyse der Mikrosektion:

✓ Sampling frequency: 1/100m²

✓ Inspection items: 20+ parameters

Spezielle Prozesskontrollen

- Impedanzkontrolle

- Microstrip: 50Ω±5%

- Stripline: 100Ω±7%

- Differential pairs: ±8%

- Thermisches Management

- Thermische Durchkontaktierungen: 0,3 mm Durchmesser

- Distribution density: 25/cm²

- Option Kupferstärke: 2oz

Anmerkung: Dieses Verfahren erfüllt die IPC-6012 Klasse 3-Normen und eignet sich für hochzuverlässige Anwendungen wie Automobilelektronik und industrielle Steuerungen. Die moderne 4-Lagen-Leiterplattenfertigung kann mit der Laserbohrtechnologie eine Leiterbahndichte von 3mil pro Raum erreichen, was einer HDI-ähnlichen Leiterbahndichte entspricht.

Design und Vorteile Analyse von 4-Lagen PCB Stackup Struktur

Grundstruktur und Schichtkonfiguration

Eine 4-Lagen-Leiterplatte (PCB) hat eine mehrschichtige Verbundstruktur, die hauptsächlich aus den folgenden Funktionsschichten besteht:

- Signalschichten: Einschließlich der Oberste Schicht and Unterste Schichtdie für das Routing verschiedener Signalwege verantwortlich sind.

- Leistungsschicht (Power Plane): Sorgt für eine stabile Stromverteilung an die Schaltungskomponenten.

- Bodenschicht (Ground Plane): Stellt das Bezugspotential des Systems her und sorgt für die elektromagnetische Abschirmung.

Zwei gängige Stackup-Konfigurationen sind weit verbreitet:

Option A: Top Layer → Power Layer → Ground Layer → Bottom Layer

- Eigenschaften: Enge Kopplung zwischen Stromversorgungs- und Erdungsebene, die eine effektive Flächenkapazität bildet und sich besonders für die Entwicklung von Hochfrequenzschaltungen eignet.

Option B: Top Layer → Ground Layer → Power Layer → Bottom Layer - Eigenschaften: Die Masseschicht schirmt die Signallagen eng ab, wodurch das Übersprechen zwischen Hochgeschwindigkeitssignalen erheblich reduziert wird.

Technische Vorteile im Detail

1. Optimierte elektrische Leistung

(1) Sicherstellung der Signalintegrität

- Niederohmige Rückleitungen über Leistungs-Masse-Ebenen reduzieren die Induktivität der Signalschleife.

- Planar capacitance effect (typically ~100pF/cm²) provides power decoupling and suppresses power noise.

- Strict impedance control (within ±10% tolerance) minimizes signal reflections.

(2) Verbesserte elektromagnetische Verträglichkeit (EMV) - Bildet einen vollständigen Faradayschen Käfig, der die Strahlungsstörung um bis zu 20dB.

- Die symmetrische Stapelung sorgt für eine gleichmäßige Verteilung des elektromagnetischen Feldes und verringert das Gleichtaktrauschen.

- Die Entkopplung von Signal- und Leistungsebenen reduziert das Übersprechen durch 30-40%.

2.Verbesserte Design-Flexibilität

- 200 %+ Anstieg an Routing-Kanälen im Vergleich zu 2-Lagen-Platten.

- Unterstützt High-Density-Interconnect (HDI) Entwürfe mit Spur/Leerzeichen bis hin zu 3/3 mil.

- Empfindliche Signale können auf den inneren Lagen verlegt werden, um eine inhärente EMI-Abschirmung zu gewährleisten.

3.Verbesserte mechanische Verlässlichkeit

- FR-4-Zwischenlagenverklebung bietet eine ausgezeichnete mechanische Festigkeit.

- Abgestimmter CTE (Wärmeausdehnungskoeffizient) Konstruktion reduziert die thermische Belastung.

- 50 %+ Verbesserung der Biegefestigkeit im Vergleich zu 2-lagigen Strukturen.

Anwendungsempfehlungen

Wichtige Überlegungen zur Gestaltung:

- Digitale Hochgeschwindigkeitsschaltungen → Prefer Option A.

- Mixed-Signal-Systeme → Recommend Option B.

- Energieintegritätskritische Anwendungen → Ensure plane spacing ≤ 0.2mm.

- Kritische Signale → Use Streifenleitungsverlegung für eine bessere Rauschunterdrückung.

Typische Anwendungen:

- Kommunikationsmittel (5G-Basisstationen, Router)

- Industrielle Kontrollsysteme

- Kfz-Elektronik

- Hochwertige Unterhaltungselektronik

Hinweis: Die aktuellen Entwürfe sollten Folgendes enthalten Impedanzanpassung und Optimierung der Stapeldicke, mit SI/PI-Simulationswerkzeuge zur Vorabprüfung empfohlen.

Anforderungen an den Herstellungsprozess für eine 4-Lagen-Leiterplatten-Stapelstruktur

1. Kritische Technologien für den Laminierungsprozess

(1) Steuerung der Prozessparameter

- Temperaturbereich: 180-200°C (material-dependent)

- Druckanforderung: 300-500 psi gleichmäßiger Druck

- Aushärtungszeit: 90-120 Minuten

(2) Qualitätskontrollpunkte

- Schicht-zu-Schicht-Ausrichtungsgenauigkeit: ≤50μm

- Stärke der Bindung: ≥1.2 N/mm²

- Leerlaufquote: <1% (Röntgenprüfung)

2.Präzisionsbohren & Beschichtungsverfahren

(1) Anforderungen an das Bohren

- Positionierungsgenauigkeit: ±25μm

- Toleranz für Lochdurchmesser: ±50μm

- Mindest-Lochgröße: 0,15 mm (mechanisches Bohren)

(2) Spezifikationen der Beschichtungsschlüssel

- Gleichmäßigkeit der Kupferdicke: ±5μm

- Lochwand Kupferdicke: ≥25μm

- Haftung der Beschichtung: Passes thermal stress test (288°C, 10s)

3.Verfahren der Oberflächenveredelung

(1) Normen für Lötstoppmasken

- Dickensteuerung: 15-25μm

- Auflösung: ≤50μm line width

- Hitzebeständigkeit: Besteht 3 Reflow-Zyklen

(2) Technische Anforderungen für den Siebdruck

- Zeichengenauigkeit: ±75μm

- Mindestlinienbreite: 0,15 mm

- Haftung: Kein Ablösen im 3M-Klebebandtest

4.Prozessvalidierung & Prüfung

(1) Testaufgaben für die Zuverlässigkeit

- Thermischer Zyklustest: -40°C to +125°C, 1000 cycles

- Luftfeuchtigkeitstest: 85°C/85% RH, 1000 hours

- Mechanischer Vibrationstest20G, 3 Achsen (je 2 Stunden)

(2) Elektrische Leistungstests

- Impedanztest: ±10% tolerance

- Isolationswiderstand: ≥100MΩ

- High-Voltage-Test: 500V DC, 60s

5.Optimierung des Herstellungsprozesses

(1) Fortgeschrittene Materialanwendungen

- Verlustarme Substrate (Dk≤3.5, Df≤0.005)

- Hoch-Tg-Materialien (Tg≥170°C)

- Halogenfreie, umweltverträgliche Materialien

(2) Modernste Prozesstechnologien

- Laserbohren (hole size ≤0.1mm)

- Any-Layer HDI-Verbindung

- Modifiziertes Semi-Additiv-Verfahren (mSAP) für feine Spuren

Anwendungsempfehlungen:

- Hochfrequenz-Schaltungen → Use low-loss material lamination

- High-Density-Designs → Laser drilling + via filling plating

- Kfz-Elektronik → Must comply with AEC-Q100 Normen

- Militär/Luft- und Raumfahrt → Recommended Dreifach-Laminierung für erhöhte Zuverlässigkeit

Anmerkung: Die Fertigung sollte folgen IPC-6012 Normen, mit kritische Prozesskontrollpunkte (CPs) für die vollständige Prozessüberwachung.

Optimierungsmethoden für den Herstellungsprozess von 4-Lagen-Leiterplatten

1. Entwurf von Optimierungsstrategien

(1) Optimierung der Stapelstruktur

- Empfohlene “S-G-P-S” Architektur (Signal-Ground-Power-Signal)

- Steuerung der wichtigsten Parameter:

- Dielectric thickness tolerance ±10%

- Impedance matching error ≤±5%

- Layer-to-layer alignment deviation ≤50μm

(2) Optimierung der Streckenführung

- Hochgeschwindigkeits-Signalverarbeitung:

- Vorrang für die Verlegung von Streifenleitungen auf der Innenseite

- Der Abstand der Differentialpaare folgt dem 3W-Prinzip

- Critical signals implement length matching (±50ps)

- Entwurf der Energieintegrität:

- Die Segmentierung der Ebene erfolgt nach der 20H-Regel

- Decoupling capacitor density: 0.1μF/cm²

2.Schlüsselkontrollen des Produktionsprozesses

(1) Normen für die Materialauswahl

- Hochfrequenzanwendungen:

- Rogers RO4003C (Dk=3,38, Df=0,0027)

- Dielectric thickness tolerance ±5μm

- Standardanwendungen:

- FR-4 TG170 Werkstoff

- Copper foil roughness Rz≤3μm

(2) Kritische Prozesskontrollen

- Laminierverfahren:

- Vacuum hot press molding (180℃/400psi)

- Interlayer resin flow control ±5%

- Metallisierung der Löcher:

- Laser drilling taper ≤5°

- Hole copper thickness ≥25μm (CPK≥1.33)

3.Lösungen zur Kostenoptimierung

(1) Verbesserung der Produktionseffizienz

- Gestaltung des Panels:

- Standard size 406mm×508mm utilization ≥85%

- Prozessrandbreite auf 3mm optimiert

- Vereinfachung der Prozesse:

- Einführung der LDI-Direktbildtechnik

- Achieve solder mask bridge ≤50μm

(2) Zusammenarbeit in der Lieferkette

- Standardisierung von Materialien:

- Einheitliche Plattenspezifikationen (0,2/0,5/1,0 mm)

- Einrichtung einer VMI-Bestandsverwaltung

- Standardisierung von Prozessen:

- Entwicklung universeller Verfahrensspezifikationen (für 90 % der Produkte)

- Erstellung einer Liste qualifizierter Lieferanten

Bewertung der Wirksamkeit der Umsetzung:

- Verbesserung der elektrischen Leistung:

- Signalintegrität um 30% verbessert

- Leistungsgeräusch um 40% reduziert

- Optimierung der Produktionskosten:

- Materialausnutzung um 15% erhöht

- Verkürzung des Produktionszyklus um 20%

- Qualität und Zuverlässigkeit:

- First-Pass-Ausbeute auf 98,5% erhöht

- MTBF auf 100.000 Stunden erweitert

Hinweis: DFM-Analysetools werden für die Vorverifizierung empfohlen, wobei eine Prozessparameterdatenbank für die kontinuierliche Optimierung erstellt wird. Hochfrequenzprodukte erfordern eine zusätzliche Überprüfung der elektromagnetischen 3D-Feldsimulation.