Inhaltsübersicht

Microvia-Technologie in hochdichten Leiterplatten

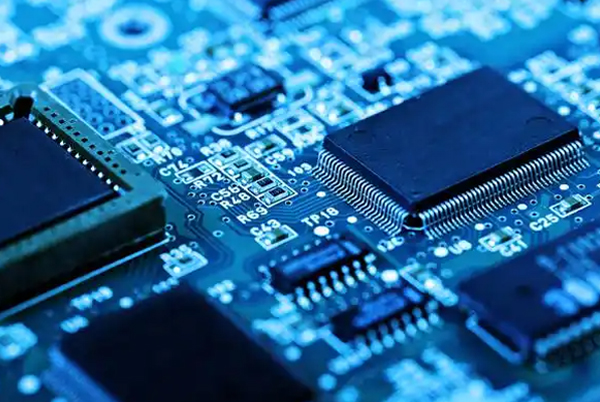

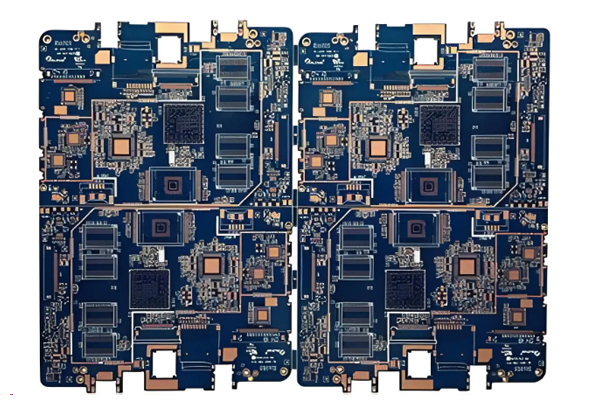

Da elektronische Geräte immer kleiner werden und die Leistungsanforderungen steigen, sind 14-Schicht Leiterplattenentwürfe werden zu einer Notwendigkeit für fortschrittliche Anwendungen. Die Microvia-Technologie steht im Mittelpunkt dieser Entwicklung und ermöglicht eine noch nie dagewesene Schaltungsdichte und Signalintegrität.

Warum Microvias für die Leistung von 14-Lagen-Leiterplatten entscheidend sind

Vorteile der Raumoptimierung

- 50% höhere Verbindungsdichte als herkömmliche Durchgangslöcher

- Ermöglicht 40% mehr Komponenten bei gleichem Platzbedarf (entscheidend für Server/5G-Anwendungen)

- Unterstützt HDI-Architekturen (High Density Interconnect)

Vorteile der Signalintegrität

| Merkmal | Verbesserung | Auswirkungen |

|---|---|---|

| Pfadlänge | 60-70% kürzer | Reduziert die Latenzzeit |

| Nebensprechen | 15-20 dB niedriger | Sauberere Signale |

| Impedanzkontrolle | ±5% tolerance | Bessere Abstimmung |

| Parasitäre Wirkungen | 40-60% Ermäßigung | Schärfere Kanten |

Durchbrüche in der Fertigung ermöglichen zuverlässige Mikrovias

Präzisions-Laserbohren

- UV-Laser (355nm) for 50-100μm microvias

- ±10μm positioning accuracy

- Mehrstufiges Bohrverfahren für 14-Schicht-Stapel

Fortgeschrittene Beschichtungstechniken

- Technologie der Direktbeschichtung

- Pulsierende Galvanik für eine einheitliche Abdeckung

- ±3μm thickness control

Lösungen für die Schichtausrichtung

- Röntgenausrichtsysteme (±25μm)

- WAK-angepasste Materialien verhindern Verzug

- Optische Passermarken für die Registrierung

Drei häufige Probleme und Lösungen beim 14-Layer PCB Microvia Design

Problem 1: Unvollständige Microvia-Beschichtung, die zu unzuverlässigen Verbindungen führt

Q: Bei der Prüfung von 14-Lagen-Leiterplatten-Prototypen weisen einige Innenlagen-Mikrovias eine unvollständige Beschichtung auf, was zu unterbrochenen Verbindungen zwischen den Lagen führt. Wie kann dies behoben werden?

ADieses Problem wird in der Regel durch drei Faktoren verursacht:

- Unzureichende Reinigung nach dem Bohrenund hinterlässt Harzrückstände, die die Kupferhaftung behindern. Lösung: Optimierung von Desmear-Verfahren durch kombinierte Plasma- und chemische Reinigung.

- Schlechter ElektrolytflussLuftblasen in tiefen Vias einschließen. Lösung: Umschalten auf oszillierende Plattierbecken zur Verbesserung des Lösungsflusses und zur Einstellung der Parameter mit Gegenstromimpuls.

- Feuchtigkeitsaufnahme in Substraten verschlechtert die Bohrqualität. Lösung: Pre-bake boards at 120°C for ≥4 hours before drilling.

Problem 2: Starke Signalreflexionen an Mikrovias in Hochgeschwindigkeitsbahnen

Q: In einem 10-Gbit/s-Hochgeschwindigkeitssignalpfad zeigen Augendiagramme erhebliche Reflexionen und Jitter beim Übergang durch Mikrovias. Wie kann dies optimiert werden?

ASignalreflexionen an Mikrovias entstehen durch Impedanzdiskontinuitäten.Die Lösungen umfassen:

- Rückwärtsbohren (Stummel entfernen): Remove unused via portions to eliminate excess copper stubs. For 14-layer boards, back-drilling depth control should be within ±50 μm.

- Optimierung der Referenzebenen: Stellen Sie sicher, dass jedes Signalmikrovia einen vollständigen Erdungsrückweg hat, idealerweise mit mindestens drei Erdungsmikrovias zur Abschirmung.

- Kompensationskondensatoren hinzufügen: Use simulation to determine optimal capacitance (typically 0.5–2 pF) to counteract parasitic inductance.

Problem 3: Durch thermische Spannungen verursachte Microvia-Risse

Q: After thermal cycling tests, some microvias—especially near board edges—develop cracks or fractures. How can this be mitigated?

A: Dies ist ein klassisches thermomechanisches Zuverlässigkeitsproblem. Die Lösungen umfassen:

- Auswahl des Materials: Use high-Tg (>170°C) substrates with matched CTE, such as Panasonic’s MEGTRON 6 or Isola’s FR408HR, which offer Z-axis CTE below 50 ppm/°C.

- Optimierung des Designs: Vermeiden Sie dichte Microvia-Anordnungen in einem Abstand von 3 mm von den Plattenkanten; verwenden Sie tropfenförmige Pads für kritische Microvias, um die mechanische Festigkeit zu erhöhen.

- Prozesskontrolle: Optimieren Sie die Laminierprofile durch schrittweises Erhitzen/Druck, um Eigenspannungen zu minimieren, und fügen Sie nach dem Aushärten ein Spannungsfreiglühen hinzu.

Best Practices für 14-Lagen PCB Microvia Design

Die Microvia-Technologie ist für elektronische Hochleistungssysteme im 14-Lagen-Leiterplatten-Design unverzichtbar geworden.Die wichtigsten Erkenntnisse aus dieser Analyse sind:

- High-Density-Verbindungen und optimiertes Signalrouting ermöglichen 14-Lagen-Leiterplatten die Integration komplexer Funktionalitäten auf kleinstem Raum und verbessern gleichzeitig die Signalintegrität.

- Erfolgreiches Microvia-Design erfordert ein Gleichgewicht zwischen elektrischer Leistung, thermomechanischer Zuverlässigkeit und Herstellbarkeit.

- Es gibt bewährte Lösungen für häufige Probleme—early risk identification and DFM (Design for Manufacturing) principles are crucial for prevention.

- Aufkommende Technologien wie Laser Direct Imaging und 3D-gedruckte Mikrovias versprechen, die Grenzen der aktuellen Designmöglichkeiten zu erweitern, insbesondere für 5G-, KI- und HPC-Anwendungen.

Für Entwicklungsteams bedeutet die Beherrschung der Microvia-Prinzipien und der Methoden zur Fehlerbehebung eine erhebliche Verbesserung der Erfolgsquote beim ersten Durchlauf, eine Beschleunigung der Entwicklungszyklen und die Sicherung eines Wettbewerbsvorteils auf sich schnell entwickelnden Märkten.

Neueste Artikel

- Der ultimative Leitfaden zum HDI-Leiterplatten-Lagenaufbau: Von grundlegenden Strukturen bis hin zu fortgeschrittenen Optimierungsstrategien

- Ausführliche Erläuterung der V-Cut-Panelization-Technologie für Leiterplatten

- Leitfaden zur Leiterplattenbestückung

- Wie Flying-Probe- und Adaptertests die Qualitätskontrollstandards für Leiterplatten neu definieren

- Beherrschung der Signalintegrität auf Leiterplatten