A medida que los productos electrónicos evolucionan rápidamente hacia la miniaturización y el alto rendimiento, la tecnología tradicional de PCB ya no puede satisfacer las crecientes demandas de densidad de cableado e integridad de la señal. PCB HDI (interconexión de alta densidad) Se ha convertido en una tecnología fundamental para implementar diseños de sistemas electrónicos complejos mediante tecnología de microvías, apilamiento multicapa y materiales avanzados. Ya sea para afrontar el reto del fan-out de los chips BGA de 0,4 mm de paso o los requisitos de integridad de la transmisión de señales de alta velocidad, un diseño de apilamiento HDI bien planificado es la clave del éxito.

Índice

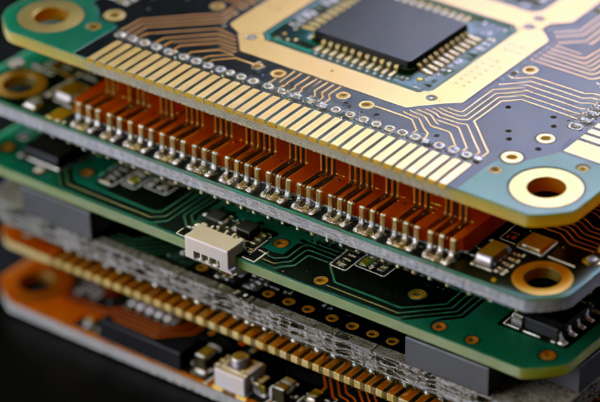

Análisis detallado de los tipos de estructuras apiladas HDI

1.1 HDI de primer orden (estructura 1+N+1)

- Características estructurales: El tipo HDI más básico, compuesto por dos capas externas (capas perforadas con láser) y un núcleo de N capas entre ellas.

- Aplicaciones típicas: Electrónica de consumo de densidad media, dispositivos IoT, controladores industriales.

- Ventajas de fabricación: Se completa en un solo ciclo de laminación, proceso maduro y alta rentabilidad.

- Ejemplo de diseño: 1+4+1 six-layer board, suitable for most applications with BGA pitch ≥0.5mm.

1.2 HDI de segundo orden (estructura 2+N+2)

- Clasificación de estructuras:

- Diseño escalonado: Las microvías en diferentes capas están desplazadas horizontalmente; un proceso sencillo y de gran fiabilidad.

- Diseño de vías apiladas: Las microvías se apilan verticalmente, lo que ahorra espacio pero requiere procesos de fabricación muy estrictos.

- Aplicaciones típicas: Placas base para teléfonos inteligentes, routers de gama alta y equipos de diagnóstico por imagen.

- Aspectos técnicosRequiere dos ciclos de laminación, admite un ancho/espaciado de línea más fino (hasta 3,0 mil/3,0 mil).

1.3 HDI de alto orden e interconexión en cualquier capa

- Estructuras de tercer orden y superiores: Adecuado para escenarios de densidad ultraalta, como chips de IA y módulos RF 5G.

- Interconexión de cualquier capa (Anylayer): Permite la conexión directa entre cualquier capa adyacente, maximizando la libertad de cableado.

- Desafíos técnicos: Require multiple laminations, precise layer-to-layer alignment (within ±10μm), and advanced plating processes.

- Consideraciones económicas: La complejidad del proceso y el coste aumentan exponencialmente con el número de laminaciones secuenciales.

Principios básicos de diseño y estrategias de optimización

2.1 Especificaciones de diseño para vías ciegas y enterradas

- Control del tamaño: The aspect ratio of blind vias should be controlled at ≤1:1 to ensure plating quality and reliability.

- Requisitos de espacio:

- Edge-to-edge spacing for blind vias of different nets: ≥9.5mil (0.24mm)

- Edge-to-edge spacing for blind vias of the same net: ≥5mil (0.13mm)

- Via-to-trace distance: Inner layer ≥6mil, outer layer ≥5-6mil

- Via-to-board-edge distance: ≥14mil (0.35mm)

- Selección del proceso:

- Los diseños de vías apiladas deben utilizar relleno de vías galvanizado para garantizar la planitud de la superficie.

- Se recomienda el taponado con resina + recubrimiento electrochapado para las vías enterradas mecánicamente, a fin de evitar el flujo de resina y la formación de huecos.

2.2 Estructura entre capas y optimización de la integridad de la señal

- Estrategia de apilamiento de capas: Las capas de señal se alternan con capas de referencia (GND/PWR).

- Estructura recomendada: Señal superior – Capa 2 tierra – Capa 3 alimentación – Capa 4 señal.

- Ventajas: Proporciona rutas de retorno de señal claras, reduce la diafonía y la radiación EMI.

- Control de la impedancia:

- Calcule con precisión las dimensiones de las microbandas y las líneas de banda, teniendo en cuenta las variaciones en los valores Dk de los materiales.

- Las señales diferenciales de alta velocidad requieren una coincidencia estricta en la longitud, un espaciado igual y un enrutamiento paralelo.

- Integridad energética:

- Evite crear «islas» al dividir los planos de alimentación para garantizar una distribución uniforme de la corriente.

- Coloque condensadores de desacoplamiento cerca de los circuitos integrados para reducir el ruido de alimentación.

2.3 Base científica para la selección de materiales

- Aplicaciones generales: La serie FR-4 satisface la mayoría de las necesidades con una buena relación calidad-precio.

- Escenarios de alta velocidad: Materiales de baja pérdida (por ejemplo, Rogers RO4835, Shengyi S1000-2M).

- Stable Dk values, low tanδ, suitable for applications above 5GHz.

- Excelente rendimiento del filamento anódico anti-conductivo (Anti-CAF).

- Necesidades de gestión térmica:

- Utilice sustratos con núcleo metálico o diseños de cobre pesado en las zonas de los dispositivos de alta potencia.

- Optimice las rutas de conducción térmica con matrices de vías térmicas.

- Consideraciones sobre la fabricabilidadEvite utilizar más de tres tipos diferentes de preimpregnados para reducir los riesgos de variación del espesor.

Puntos clave del diseño para la fabricabilidad (DFM)

3.1 Optimización del proceso de laminación

- Minimizar los ciclos de laminación: Reducir los ciclos de laminación optimizando la ubicación de las vías enterradas.

- Ejemplo: Cambiar las vías enterradas de las capas 3-6 a las capas 2-7 puede eliminar un ciclo de laminación.

- Estrategia de laminación: La laminación secuencial es preferible a la laminación en un solo paso para reducir las burbujas y los huecos.

- Diseño simétrico: Recuento uniforme de capas y distribución simétrica del material para reducir el riesgo de deformación.

3.2 Limitaciones de fabricación y adaptación del diseño

- Capacidad de perforación láser: Tamaño mínimo del orificio: 0,1 mm (estándar), 0,075 mm (límite).

- Límites de ancho y espaciado de línea: 3,0 mil/3,0 mil, cumpliendo con los requisitos de enrutamiento de alta densidad.

- Precisión de alineación: Layer-to-layer alignment must be controlled within ±10μm to ensure microvia connection reliability.

- Acabado superficial: El relleno electrochapado garantiza una superficie plana del via ciego, evitando defectos de soldadura.

3.3 Estrategias de control de costes

- Simplificación de la estructura: Elija la estructura de apilamiento más simple que cumpla con los requisitos de rendimiento.

- IDH localizado: Utilice vías ciegas/enterradas complejas solo en áreas clave como BGA, manteniendo las demás áreas tradicionales.

- Estandarización del diseño: Siga los parámetros de proceso estándar del fabricante para evitar los costes derivados de la personalización.

- Colaboración temprana: Comunique las capacidades del proceso al fabricante de PCB (por ejemplo, TOPFAST) durante la fase de diseño para reducir la necesidad de reelaborar el diseño.

Mejores prácticas y tendencias del sector

4.1 Análisis de casos exitosos

- Placa base para teléfonos inteligentes: HDI de segundo orden con diseño de vías escalonadas, que permite una salida en abanico BGA de 0,4 mm, equilibrando rendimiento y coste.

- Módulo de estación base 5G: Materiales dieléctricos híbridos, utilizando Rogers para las áreas de RF y FR-4 para las áreas digitales.

- Sistema ADAS para automóviles: Diseño HDI de alta fiabilidad, que cumple con los requisitos de ciclos de temperatura y vibración de grado automotriz.

4.2 Tendencias de desarrollo futuro

- Tecnología de línea ultrafina: Avanzando hacia un ancho/espaciado de línea de 2,0 mil/2,0 mil.

- Componentes integrados: Las resistencias y los condensadores están integrados en la placa de circuito impreso, lo que aumenta aún más la densidad.

- Diseño modular: Diseñar áreas HDI complejas como módulos estándar para mejorar la reutilización del diseño.

- Herramientas de simulación inteligente: Optimización de apilamiento impulsada por IA y predicción de integridad de la señal.

Guía práctica para ingenieros

5.1 Proceso de diseño recomendado

- Análisis de requisitosAclarar la velocidad de la señal, los requisitos de densidad y los objetivos de coste.

- Selección de estructura: Elija el orden HDI en función del paso BGA y el número de E/S.

- Selección de materiales: Seleccione los materiales dieléctricos en función de la frecuencia, la pérdida y las necesidades térmicas.

- Diseño apilable: Utilice herramientas profesionales para el cálculo de la impedancia y la optimización de la secuencia de capas.

- Verificación DFMConfirme la viabilidad del proceso y las normas de diseño con el fabricante.

- Pruebas de prototipos: Fabricar muestras y realizar pruebas exhaustivas de integridad y fiabilidad de la señal.

5.2 Problemas comunes y soluciones

- Problema: Huecos en el cromado ciego.

Solución: Control aspect ratio ≤1:1, optimize plating parameters. - Problema: Deformación excesiva tras la laminación.

Solución: Adoptar una apilación simétrica, controlar el equilibrio de la densidad del cobre. - Problema: Atenuación excesiva de señales de alta velocidad.

SoluciónCambiar a materiales de baja pérdida, optimizar la estructura de la línea de transmisión.

5.3 Puntos clave para la colaboración con los fabricantes

- Proporcione diagramas completos de apilamiento y especificaciones de materiales.

- Identifique claramente las redes de señales críticas y los requisitos de impedancia.

- Comparta la intención del diseño y las expectativas de rendimiento para obtener recomendaciones sobre el proceso.

- Tenga en cuenta las áreas de especialización del fabricante, como la experiencia de TOPFAST en la fabricación de HDI de volumen pequeño a mediano.

Conclusión

El diseño de apilamiento de PCB HDI es un arte técnico que consiste en encontrar el equilibrio óptimo entre densidad, rendimiento, fiabilidad y coste. A medida que avanzan las tecnologías 5G, inteligencia artificial e IoT, el HDI evoluciona hacia una mayor densidad, mayor velocidad y mayor integración. El éxito del diseño HDI no solo depende de herramientas y métodos de diseño avanzados, sino también de una estrecha colaboración con fabricantes de PCB experimentados, como TOPFAST. Desde la consulta de diseño en las primeras etapas hasta la optimización del proceso de fabricación, los fabricantes profesionales proporcionan un apoyo técnico y una orientación sobre los procesos esenciales, lo que ayuda a los ingenieros a transformar de manera eficiente diseños complejos en productos fiables.

Problemas comunes en el diseño de PCB HDI

A: Causas: Discontinuidad de impedancia, selección inadecuada de materiales de apilamiento o diseño subóptimo de estructuras de vías ciegas.

Recomendaciones:

Adopte una estructura apilada de línea de banda estrecha (capas de señal intercaladas entre dos planos de referencia).

Priorizar materiales de baja pérdida (por ejemplo, Shengyi S1000-2M o la serie Rogers).

Realizar análisis exhaustivos de simulación SI/PI en rutas de señales críticas.

Verifique la precisión del modelo de impedancia de apilamiento con el fabricante (por ejemplo, TOPFAST).

A: Causas: Densidad excesiva de pines (por ejemplo, BGA de 0,4 mm), en la que las vías convencionales no pueden cumplir los requisitos de enrutamiento.

Recomendaciones:

Implementar la tecnología Via-in-Pad Plated Over (VIPPO), perforando directamente con láser vías en almohadillas.

Adopte un diseño de vía ciega escalonada (por ejemplo, vías escalonadas de 1-2 capas y 2-3 capas).

Configure canales de enrutamiento de escape dedicados alrededor de la periferia del BGA.

Confirme previamente con el fabricante el diámetro mínimo y las capacidades del anillo anular de la almohadilla.

A: Causas: Vías de disipación del calor insuficientes para componentes de alta potencia y distribución desigual del espesor del cobre.

Recomendaciones:

Design thermal via arrays (via diameter ≥ 0.3mm) beneath heat-generating components.

Utilice cobre de 2 oz o más grueso para las planas eléctricas.

Para requisitos térmicos extremos, consulte al fabricante (por ejemplo, TOPFAST) sobre sustratos con núcleo metálico o soluciones con bloques de cobre integrados.

Realizar pruebas de termografía infrarroja en placas prototipo para analizar la distribución del calor.