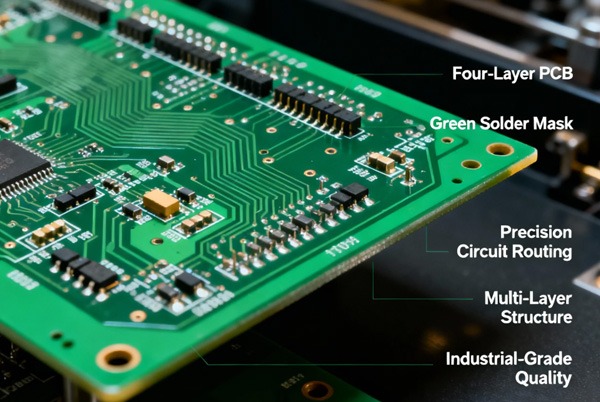

En la electrónica de consumo, los equipos de control industrial y los sistemas digitales de alta velocidad, las placas de circuito impreso de cuatro capas son muy apreciadas por su excelente compatibilidad electromagnética (EMC), integridad de la alimentación e integridad de la señal.

Índice

Placa de circuito impreso de 4 capas Estructura apilada

El diseño del apilamiento es la base del rendimiento de una placa de 4 capas. Un apilamiento inadecuado puede provocar diafonía de señales, ruido en la fuente de alimentación e incumplimiento de las normas EMI.

1. Comparación de esquemas clásicos de apilamiento

- Esquema 1 (recomendado)

- Capa superior: Capa de señal

- Capa 2: Plano de tierra (GND)

- Capa 3: Plano de alimentación (PWR)

- Capa inferior: Capa de señal

- Ventajas: El plano de tierra proporciona una referencia sólida para las señales de la capa superior. Los planos de alimentación y tierra adyacentes forman una capacitancia de desacoplamiento inherente.

- Esquema 2

- Capa superior: Capa de señal

- Capa 2: Plano de alimentación

- Capa 3: Plano de tierra

- Capa inferior: Capa de señal

- Escenarios aplicables: Dispositivos de alta corriente (por ejemplo, controladores de motores). Tenga en cuenta los posibles cambios en el plano de referencia para las señales de la capa inferior.

- Esquema 3 (Usar con precaución)

- Capa superior: plano de tierra

- Capa 2: Capa de señal

- Capa 3: Capa de señal

- Capa inferior: plano de potencia

- Riesgos: Plano de tierra incompleto, rutas de retorno de señal largas. Adecuado principalmente para placas de baja frecuencia con predominio de conectores.

2. Configuración de los parámetros clave

- Espesor dieléctrico: Recommended 0.1–0.2mm between signal and reference planes to enhance inter-layer coupling.

- Peso del cobre: Outer layers 1oz (35μm), inner layers 0.5oz (17.5μm). Can increase to 2oz for high-current areas.

- Diseño de retroceso: Power planes should be indented 40–80mil relative to the ground plane (20H rule) to reduce edge radiation.

Vía Diseño

Las vías son cruciales para las conexiones entre capas, pero introducen parámetros parásitos que afectan a las señales de alta velocidad.

1. Mediante selección de tipo

- Vías pasantes: Bajo coste, adecuado para señales estándar y conexiones de alimentación.

- Vías ciegas/enterradas: Se utiliza para el enrutamiento de escape BGA de alta densidad, pero aumenta el coste del proceso.

2. Cálculo de parámetros parasitarios

- Capacitancia parásita:

C ≈ 1.41ε · T · D1 / (D2 - D1)

¿Dónde?Tes el grosor de la tabla,D1es el diámetro del taladro,D2es el diámetro de la almohadilla. - Inductancia parásita:

L ≈ 5.08h [ln(4h / d) + 1]

¿Dónde?hes a través de la longitud,des el diámetro del taladro.

3. Directrices de uso de Via

- Vías de alimentación: Utilice vías más grandes (por ejemplo, 12 mil de diámetro/16 mil de perforación) y coloque varias en paralelo para reducir la impedancia.

- Vías de señal: Prefiera vías más pequeñas (por ejemplo, 8 mil de diámetro/12 mil de perforación). Evite la colocación asimétrica en pares diferenciales.

- Vías térmicas: Colocar debajo de componentes que generan calor (por ejemplo, broca de 0,3 mm, paso de 1,5 mm).

Enrutamiento de PCB

1. Procedimiento de enrutamiento

- Aborda primero las áreas difíciles: Comience el enrutamiento desde áreas complejas como BGA e interfaces de alta velocidad.

- Manipulación modular: Ruta por bloques funcionales (por ejemplo, MCU, memoria, circuitos analógicos) para evitar interferencias cruzadas.

- Ruta de limpieza: Enrute las señales de baja velocidad en último lugar, optimizando la utilización del canal mediante el ajuste del ancho y el espaciado de las pistas.

2. Reglas críticas de enrutamiento

- Control de impedancia:

- Single-ended: 50Ω. Differential pairs: 100Ω.

- Consíguelo ajustando el ancho de traza, el grosor dieléctrico y la permitividad.

- Manejo de señales de alta velocidad:

- Priorizar el enrutamiento de las señales de reloj en las capas internas, con referencia a un plano de tierra.

- Maintain length matching in differential pairs (≤5mil tolerance).

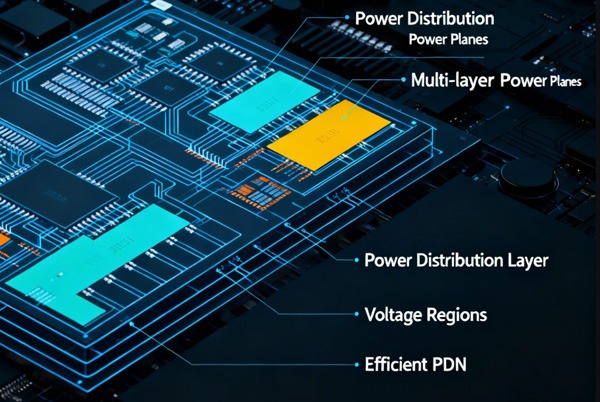

- Segmentación del plano de potencia:

- Segmentar un único plano de alimentación en un máximo de 3 regiones (por ejemplo, 3,3 V, 5 V, 12 V).

- Use segmentation lines ≥0.5mm wide to prevent creepage issues.

Diseño de integridad de potencia

1. Colocación del condensador de desacoplamiento

- Selección: 0.1μF ceramic capacitors (high-frequency) + 10μF tantalum capacitors (low-frequency).

- Ubicación: Position close to IC power pins (≤3mm). Connect directly to power/ground planes via vias.

2. Integridad del plano de tierra

- Evite dividir el plano de tierra con trazas de señal para garantizar rutas de retorno de baja impedancia.

- Connect digital and analog grounds at a single point using a ferrite bead or 0Ω resistor.

Verificación del diseño y preparación de la producción

1. Lista de verificación de la RDC

- Trace Width/Spacing: General signals ≥6/6mil, Power traces ≥12/12mil.

- Drill-to-Copper Distance: ≥8mil to prevent short circuits.

2. Simulación de integridad de la señal

- Utilice herramientas como HyperLynx o Sigrity para comprobar el tiempo de subida, el oscilación y la continuidad de la impedancia.

- Céntrese en verificar los relojes, las señales diferenciales y la ondulación de la fuente de alimentación.

3. Salida del archivo de producción

- Proporcione archivos Gerber (incluye capas, máscara de soldadura, taladro), cupones de prueba de impedancia y planos de montaje.

Conclusiones clave sobre el diseño

- Esquema de apilamiento preferido 1, asegurando un plano de tierra adyacente a las capas de señal primarias.

- Equilibrar el coste y el rendimiento a través del diseño., utilizando vías de alimentación paralelas para reducir la impedancia.

- Ruta que sigue el principio «Difícil primero», dando prioridad a las señales de alta velocidad en las capas internas.

- Limitar la segmentación de la energía a 3 regiones., colocando condensadores de desacoplamiento cerca de los circuitos integrados.

- Validar con DRC y simulación. para evitar tener que volver a trabajar en la posproducción.