Bajo la tendencia de alta velocidad y miniaturización de los equipos electrónicos modernos, diseño de PCB multicapa se enfrenta a retos sin precedentes. En este artículo, analizaremos la tecnología clave de las vías ciegas, desde los principios básicos hasta las aplicaciones prácticas, para revelar cómo resolver los problemas de integridad de la señal en el diseño de alta velocidad mediante vías ciegas.

Índice

Taladrado de placas de circuito impreso Tecnología Placa de circuito impreso ordinaria Visión general

Perforación mecánica: Tradicional pero indispensable

- Diámetro de orificio adecuado: Normalmente superior a 0,15 mm

- Material de la broca:Acero al tungsteno o diamantado

- Ventaja de costes:Precio unitario extremadamente bajo para la producción en serie

- Limitaciones:Dificultad en el procesamiento de microvías, restricciones en el tamaño mínimo de los orificios.

Taladrado Láser:La elección preferida para alta precisión

- Láser de CO2: Suitable for 50-150μm hole diameters, fast processing speed

- Láser UV: Can process 20-50μm ultra-micro vias with higher precision

- Características: Procesamiento sin contacto, sin tensión mecánica

Tecnologías de perforación especiales

- Perforación por plasma: Se utiliza para tableros flexibles y materiales especiales

- Perforación por chorro de agua: Sin zona afectada por el calor, adecuado para materiales sensibles

- Taladrado compuesto mecánico-láser: Combina las ventajas de ambos para el procesado de cartón grueso

Análisis en profundidad del proceso de agujeros ciegos

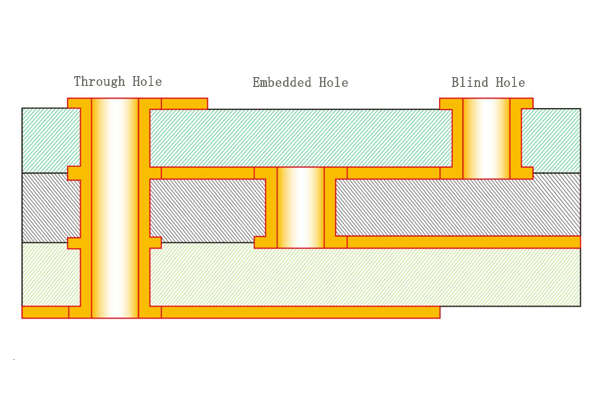

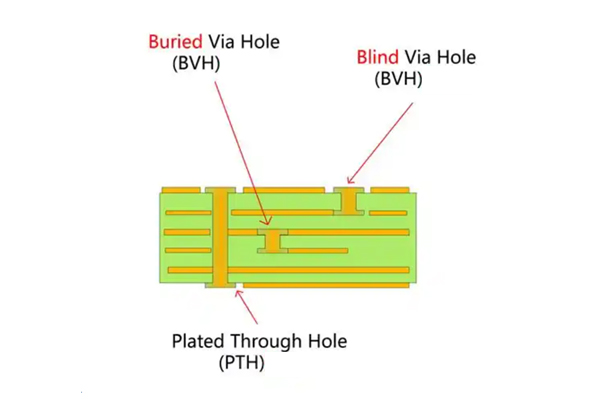

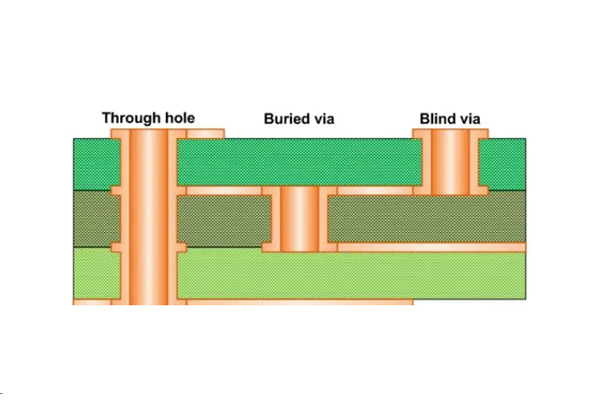

¿Qué es un agujero ciego?

Blind vias are vias that extend from the surface of the PCB to an internal layer only and do not run through the entire board, like a “zone elevator” in a tall building that stops at a specific floor instead of going to all floors. This selective connectivity revolutionizes high-speed design.

Vía ciega frente a orificio pasante: comparación de rendimiento

| Métrica | Vía ciega | Orificio pasante |

|---|---|---|

| Longitud del trayecto de la señal | 30-70% más corto | Penetración total |

| Nivel de diafonía | 40-60% menos | Relativamente alto |

| Densidad de cableado | 2-3 veces mayor | Nivel básico |

| Coste de fabricación | 20-50% más | Coste de referencia |

Principales ventajas del proceso de las vías ciegas

Mejora de la integridad de la señal: Las vías ciegas acortan considerablemente el trayecto de transmisión de la señal, reduciendo las reflexiones y pérdidas de señal. Los estudios han demostrado que las reflexiones de señal pueden reducirse en más de un 40% con las vías ciegas.

EMC mejorada: Al eliminar las penetraciones innecesarias a través de los orificios, las vías ciegas reducen eficazmente las interferencias electromagnéticas (EMI) y la diafonía de señales, lo que resulta especialmente crítico en aplicaciones de alta frecuencia en la clase GHz.

Mayor libertad de diseño: Las vías ciegas liberan un valioso espacio de cableado, lo que permite a los ingenieros realizar diseños de interconexión más complejos en un área más pequeña.

Aumento de la miniaturización del producto: En comparación con los diseños de orificios pasantes, el proceso de vías ciegas ahorra hasta un 30% de espacio en la placa, lo que constituye la base técnica para adelgazar los dispositivos electrónicos modernos.

Explicación detallada del proceso de fabricación de vías ciegas

1. Etapa de alineación de precisión

- Sistema de posicionamiento láser: Uses CCD visual alignment with ±5μm accuracy

- Compensación de la contracción: Precompensa 0,05-0,1% en función de las propiedades del material

- Marcas de referencia: Diseños 3-5 objetivos globales de alineación

2.Controles clave en el taladrado láser

- Control de la energía: Utiliza tecnología de ajuste del gradiente de energía pulsada

- Enfoque de gestión: El enfoque dinámico en el eje Z garantiza la coherencia entre capas

- Sistema de eliminación de polvo: La aspiración en tiempo real evita la redeposición de residuos

Ejemplos de parámetros típicos:

- Láser UV: 355 nm de longitud de onda, 20 ns de ancho de pulso

- For 100μm diameter: Single hole processing time ≈3ms

- Repositioning accuracy: ±3μm

3.Vía Proceso de tratamiento de muros

- Limpieza por plasma:

- Gas mixture: O₂(80%)+CF₄(20%)

- Potencia: 300-500W

- Duración: 45-90 segundos

- Micrograbado químico:

- Sistema ácido sulfúrico-peróxido de hidrógeno

- Controls copper surface roughness at 0.2-0.5μm

4.Pasos clave de la metalización

- Cobreado químico:

- Thickness: 0.3-0.8μm

- Deposition rate: 2-4μm/h

- Espesamiento galvánico:

- Utiliza tecnología de chapado por impulsos

- Target thickness: 15-25μm

- Uniformity control: ≤10%

5.Optimización de la transferencia de patrones

- Imagen directa láser (LDI):

- Resolution: 10μm line width/spacing

- Alignment accuracy: ±8μm

- Laminado en seco:

- Presión: 0,4-0,6MPa

- Temperature: 100-110℃

Soluciones a cinco problemas prácticos comunes

P1: ¿Cómo evitar la depresión de la resina en las vías ciegas?

A: La depresión de la resina suele deberse a una energía de perforación excesiva o a materiales sensibles al calor. Recomendaciones:

- Optimice los parámetros del láser:Reducir la energía de un solo pulso, aumentar el número de pulsos

- Switch to high-Tg materials: e.g., Isola 370HR (Tg=180℃)

- Tratamiento posterior:Utilización mediante chapado de relleno o relleno adhesivo conductor

P2: ¿Cómo resolver la discontinuidad de impedancia cuando las señales de alta frecuencia pasan a través de vías ciegas?

A:Soluciones para la discontinuidad de impedancia:

- Compensación de diseño:Añadir antialmohadillas en los cuellos de las vías

- Optimización estructural:Utilización de vías ciegas cónicas (superior más grande, inferior más pequeña).

- Selección del material:Utilizar materiales de baja variación de densidad (por ejemplo, Rogers RO4835).

- Verificación por simulación:Optimización previa con HFSS o CST

P3: ¿Cómo abordar las importantes fluctuaciones de rendimiento en ciego mediante la producción en serie?

A:Estabilizar el rendimiento requiere un control sistemático:

- Mantenimiento del equipo:Calibración diaria de la trayectoria óptica del láser

- Control de parámetros:Registro en tiempo real de parámetros clave (energía, enfoque, etc.)

- Inspección del primer artículo:Análisis transversal de cada lote

- Control SPC:Establecer gráficos de control para parámetros clave (por ejemplo, diámetro CPK>1,33).

P4: ¿Cómo resolver la desalineación entre capas en placas HDI con vías ciegas y enterradas apiladas?

A:Soluciones para la alineación de vías apiladas multicapa:

- Correspondencia de materiales: seleccione materiales de baja contracción (por ejemplo, MEGTRON6).

- Optimización del proceso: Utilizar la tecnología de laminación secuencial

- Diseño de alineación:Añadir objetivos de alineación óptica

- Algoritmo de compensación:Compensación dinámica basada en datos previos de contracción de la laminación.

P5: ¿Cómo reducir los costes de fabricación de vías ciegas en placas de circuito impreso de 8 capas o más?

A:Estrategias de control de costes para placas de gran número de capas:

- Optimización del diseño:Reducción de las vías ciegas innecesarias

- Combinación de procesos:Utilizar vías ciegas para las capas de señales críticas y orificios pasantes para las demás.

- Consolidación de lotes:Compartir paneles de producción con otros pedidos

- Colaboración con los fabricantes:Involucre a los fabricantes de placas de circuito impreso desde el principio en las revisiones de diseño.

Técnicas de proceso avanzadas

Reglas de oro para los parámetros de taladrado láser

- Perforación de la capa de cobre: Alta energía + impulso corto (por ejemplo, 1mJ/10ns)

- Perforación de la capa dieléctrica: Baja energía + pulso largo (por ejemplo, 0,5mJ/20ns)

- Materiales mixtos: Utilizar algoritmos de gradiente de energía

Técnicas especiales de tratamiento de las vías ciegas

- Vías ciegas recubiertas de cobre: Las protuberancias superficiales de cobre mejoran la fiabilidad de la soldadura

- Vías ciegas rellenas: El relleno de cobre galvánico mejora la conducción térmica

- Vías ciegas escalonadas: La combinación de diferentes profundidades de capa optimiza la utilización del espacio

Puntos clave de verificación de la fiabilidad

- Pruebas de estrés térmico: -55℃~125℃ cycling for 1000 cycles

- Pruebas IST: Pruebas de resistencia actuales para 500 ciclos

- Análisis transversal: Inspeccionar la uniformidad del espesor del cobre de la pared de la vía

- Pruebas de impedancia: TDR measurement for impedance consistency (±10%)

Casos prácticos de aplicaciones industriales

Caso 1: Módulo de antena de onda milimétrica 5G

- Reto: 77GHz requisito de pérdida de transmisión de señal <0,3dB/pulgada

- Solución:

- Adopta un diseño de persiana cónica de 1-2 capas

- Material Rogers RO3003 usado

- Tratamiento con plasma añadido tras la perforación con láser

- Resultados: 42% de reducción de la pérdida de inserción, 15% de mejora de la eficacia de la antena

Caso 2: GPU de computación de alto rendimiento

- Reto: Implementación de enrutado de escape BGA de 0,4 mm en una placa de circuito impreso de 16 capas

- Innovaciones:

- Diseño de vía ciega escalonada de 1-3-5 capas

- Perforación directa láser combinada con perforación mecánica

- Metalizado de relleno de vías para planarización

- Resultados: Aumento del 60% de los canales de enrutamiento, velocidad de señalización de 32 Gbps.

Futuras fronteras tecnológicas

Tecnología de perforación fotónica:

- Aplicaciones del láser de femtosegundo: Reducir las zonas afectadas por el calor

- Planificación inteligente de la trayectoria de perforación:Secuencia de procesamiento optimizada por IA

- Sistemas de inspección en línea:Medición de topografía 3D durante el procesamiento

Direcciones para la innovación de materiales:

- Materiales dieléctricos de baja pérdida procesables por láser

- Tecnología de relleno de vías con pasta de cobre nanocompuesta

- Capa molecular autoensamblada mediante tratamiento mural

Más lecturas relacionadas

Taladrado de placas de circuito impreso Tecnología Placa de circuito impreso ordinaria