Placas de circuito impresso (PCBs) são os pilares fundamentais dos dispositivos eletrônicos modernos. À medida que os dispositivos tendem a frequências mais altas, velocidades mais altas e miniaturização, um excelente projeto de layout de PCB tornou-se um fator crítico para determinar o desempenho do produto. Este artigo aprofunda técnicas avançadas de layout de PCB, como roteamento de alta velocidade, controle de impedância e otimização da integridade de energia, ajudando os engenheiros a projetar placas de circuito mais confiáveis e eficientes.

Índice

Tecnologia de roteamento de alta velocidade

Princípio do traço curto e reto

O roteamento de sinais de alta velocidade deve seguir o princípio do shoCaminho de teste, minimizando curvas e voltas desnecessárias. Manter uma geometria de traço consistente reduz significativamente o risco de atraso e distorção do sinal.

Pontos-chave da implementação:

- Priorize o roteamento de caminhos de sinal críticos de alta velocidade.

- Evite usar ângulos de 90 graus; em vez disso, use ângulos de 45 graus ou curvas em arco.

- Mantenha uma largura e um espaçamento uniformes entre os traços.

Estratégia de roteamento de pares diferenciais

O roteamento diferencial de sinais é um método eficaz para combater Interferência eletromagnética (EMI) e interferência:

| Vantagens | Método de implementação |

|---|---|

| Forte rejeição de ruído de modo comum | Mantenha uma correspondência rigorosa do comprimento para pares diferenciais. |

| Radiação EMI reduzida | Controle o espaçamento consistente dentro do par diferencial. |

| Integridade do sinal aprimorada | Evite divisões nos planos de referência sob pares diferenciais. |

Otimização do layout dos componentes

A colocação estratégica dos componentes pode reduzir significativamente a área do loop de sinal:

- Layout da partição de acordo com os módulos funcionais.

- Reduza as distâncias de interconexão entre dispositivos de alta velocidade.

- Evite a proximidade entre linhas de sinal sensíveis e fontes de ruído.

Tecnologia de controle de impedância

Relação entre largura do traço e impedância

Atinja a impedância característica desejada por meio de cálculos precisos e ajustes na largura do traço:

Estratégias comuns de controle de impedância:

- Uso ferramentas de cálculo de impedância para uma simulação precisa.

- Considere a estrutura de empilhamento da placa de circuito impresso e as propriedades do material dielétrico.

- Defina metas de impedância correspondentes para diferentes tipos de sinal.

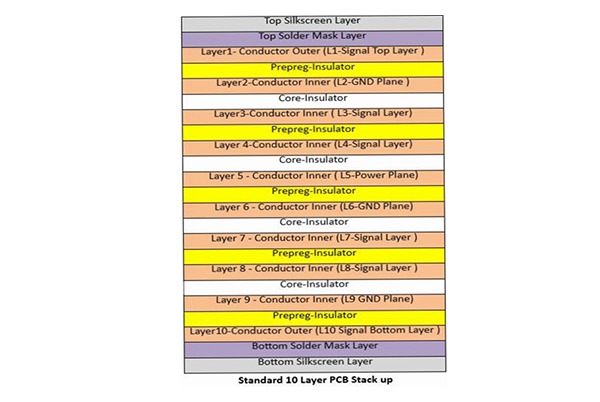

Otimização do projeto de empilhamento

Um projeto racional de empilhamento garante impedância consistente em toda a placa:

Recomendado Empilhamento de 4 camadas Estrutura:

Camada superior: Camada de sinal (estrutura microstrip)

Camada 2: Plano de aterramento

Camada 3: Plano de alimentação

Camada inferior: Camada de sinal (estrutura stripline)Seleção de material dielétrico

Selecionando materiais dielétricos estáveis é crucial para o controle da impedância:

- Preste atenção à constante dielétrica (Dk) e ao fator de dissipação (Df) do material.

- Considere a estabilidade da temperatura e as características de frequência.

- Priorize materiais de baixa perda para aplicações de alta frequência.

Otimização da integridade da energia

Estratégia de layout do capacitor de desacoplamento

Os capacitores de desacoplamento são a primeira linha de defesa para manter a estabilidade da energia:

Esquema de desacoplamento gradual:

- Bulk Capacitors (10-100μF): Colocado nos pontos de entrada de energia para lidar com flutuações de baixa frequência.

- Medium Capacitors (0.1-1μF): Distribuído por toda a placa para cobrir a faixa de frequência média.

- Small Capacitors (0.01-0.1μF): Colocado próximo aos pinos de alimentação do dispositivo para suprimir ruídos de alta frequência.

Rede de distribuição de energia (PDN) de baixa impedância

Métodos para construir uma PDN de baixa impedância:

- Use planos sólidos de alimentação e aterramento.

- Use vias com prudência para conectar a alimentação entre diferentes camadas.

- Reduza a indutância em série no caminho de alimentação.

Simulação de integridade de energia

Use ferramentas como SPICE e HyperLynx para simulação em fase inicial:

- Identifique possíveis problemas de ruído de energia.

- Otimize a quantidade e a colocação dos capacitores de desacoplamento.

- Verifique a queda de energia e a margem de ruído.

Métodos de mitigação de EMI/EMC

Otimização da técnica de aterramento

O aterramento adequado é a base do projeto EMC:

Pontos-chave do projeto de aterramento:

- Use planos de aterramento contínuos e sólidos.

- Forneça o caminho de retorno mais curto para sinais de alta frequência.

- Evite rachaduras e lacunas no plano de aterramento.

Técnicas de blindagem e filtragem

Use uma combinação de métodos para suprimir a interferência eletromagnética:

| Tipo de técnica | Cenário do aplicativo | Método de implementação |

|---|---|---|

| Blindagem | Proteção de circuitos sensíveis | Escudos metálicos, revestimentos condutores |

| Filtragem | Supressão de interferência conduzida | Filtros EMI, contas de ferrite |

| Rescisão | Reduzindo reflexos | Resistores de correspondência de fonte/extremidade |

Estratégias de gerenciamento térmico

Projeto e layout do dissipador de calor

- Selecione dissipadores de calor com tamanho adequado com base na dissipação de energia.

- Garanta um bom contato entre o dissipador de calor e a superfície do chip.

- Considere alinhar a orientação do dissipador de calor com a direção do fluxo de ar.

Vias térmicas e almofadas térmicas

- Organize matrizes de vias térmicas sob componentes geradores de calor.

- Use thermal pads to increase the散热 area.

- Conduza eficazmente o calor para os planos de aterramento internos.

Gerenciamento do fluxo de ar

- Considere os caminhos do fluxo de ar durante a colocação dos componentes.

- Coloque os componentes de alta temperatura a montante no fluxo de ar.

- Evite componentes altos que bloqueiem as vias de fluxo de ar.

Princípios do Design para Fabricação (DFM)

Pontos-chave do DFM

A implementação dos princípios do DFM pode melhorar significativamente a eficiência e o rendimento da produção:

Itens críticos de verificação DFM:

- A largura mínima do traço/espaçamento está em conformidade com as capacidades do fabricante.

- Tamanhos e posições otimizados dos furos de perfuração.

- Máscara de solda padronizada e design de serigrafia.

- Consideração do design da borda da placa e da panelização.

Utilizando ferramentas avançadas de DFM

- Use ferramentas como PCBCart DFM instantâneo para verificação prévia do projeto.

- Obtenha feedback em tempo real sobre a capacidade de fabricação.

- Identifique e corrija possíveis problemas antecipadamente.

Considerações especiais para o layout de PCB de sinal misto

Particionamento analógico e digital

Lidar corretamente com a relação entre circuitos analógicos e digitais:

Princípios de layout de particionamento:

- Separe fisicamente as áreas dos circuitos analógicos e digitais.

- Use planos de alimentação e aterramento independentes.

- Implemente aterramento de ponto único em dispositivos ADC/DAC.

Estratégias de aterramento de sinal misto

Escolha o esquema de aterramento adequado com base na complexidade do sistema:

Esquema de plano de aterramento único (Adequado para sistemas com baixa corrente digital):

- Use um único plano de aterramento contínuo.

- Permita que as correntes de retorno analógicas e digitais se separem naturalmente.

Esquema de plano de terra dividido (Adequado para sistemas com alta corrente digital):

- Separe os aterramentos analógicos e digitais.

- Conecte em um único ponto próximo à fonte de alimentação (aterramento em estrela).

- Forneça caminhos de aterramento claros para dispositivos de sinal misto.

Lista de verificação do layout da placa de circuito impresso

Use a seguinte lista de verificação para a verificação final após concluir o layout:

- Verificação da integridade do sinal (caminhos de sinal de alta velocidade, terminação, impedância)

- Verificação da integridade da energia (desacoplamento, impedância PDN)

- Avaliação da gestão térmica (dissipação de calor para componentes de alta potência, fluxo de ar)

- Considerações sobre EMC (blindagem, filtragem, aterramento)

- Verificação DFM (limitações do processo, tolerâncias)

- Viabilidade da montagem (espaçamento dos componentes, requisitos de soldagem)

- Acesso para teste e retrabalho (pontos de teste, acesso à sonda)

Conclusão

Dominar técnicas avançadas de layout de PCB é fundamental para projetar dispositivos eletrônicos de alto desempenho e alta confiabilidade. Ao implementar o roteamento de alta velocidade, o controle de impedância, a otimização da integridade de energia e as estratégias de gerenciamento térmico apresentadas neste artigo, os engenheiros podem melhorar significativamente o desempenho do produto, reduzindo os custos de produção e melhorando o rendimento. À medida que os dispositivos eletrônicos evoluem para frequências mais altas e tamanhos menores, essas técnicas avançadas de layout se tornarão cada vez mais importantes.