Cartes de circuits imprimés (PCB) servent d'épine dorsale aux appareils électroniques modernes, leurs avancées en matière de fabrication ayant un impact direct sur la performance et la fiabilité des produits. Avec le développement rapide de la 5G, de l'IoT, de l'IA et d'autres technologies de pointe, l'industrie des PCB connaît une innovation sans précédent. Cet article fournit une analyse approfondie des principales technologies de fabrication des PCB, de leurs applications et des tendances futures, offrant une compréhension complète de ce domaine spécialisé.

Table des matières

Aperçu des processus de fabrication des circuits imprimés

PCB manufacturing has evolved from simple single-layer boards to today’s high-density interconnect (HDI) multilayer boards, continuously pushing the limits of physical design. The three primary PCB manufacturing processes are:

Processus soustractif: La méthode la plus traditionnelle, qui consiste à appliquer une résine photosensible sur un stratifié recouvert de cuivre, à l'exposer pour créer un schéma de circuit, puis à le graver pour éliminer le cuivre non protégé. Bien que mature, ce procédé a une précision limitée et peine à répondre aux exigences modernes de l'IDH.

Processus entièrement additif (SAP): Utilise un substrat isolant avec un catalyseur photosensible. Après une exposition sélective, le cuivre est déposé chimiquement uniquement aux endroits nécessaires pour former les circuits. Ce procédé permet une grande précision, mais exige un contrôle rigoureux des matériaux et des processus.

Processus semi-additif modifié (mSAP): Combine les avantages des méthodes soustractives et additives. Une fine couche de cuivre est déposée chimiquement, puis électrodéposée de manière sélective pour épaissir les traces du circuit, avant que l'excès de cuivre ne soit éliminé par gravure. Ce procédé est idéal pour les circuits ultrafins et est devenu une technologie courante pour les circuits imprimés haut de gamme.

Principales technologies avancées de fabrication de circuits imprimés

Via-in-Pad : Permettre des interconnexions à haute densité

La technologie Via-in-pad consiste à placer des vias conducteurs directement à l'intérieur des plots des composants, ce qui permet d'améliorer considérablement l'utilisation de l'espace des circuits imprimés.

Principaux avantages:

- Permet d'économiser plus de 30 % d'espace sur la carte, idéal pour les conceptions compactes

- Raccourcit le trajet des signaux, améliorant ainsi les performances des circuits à grande vitesse

- Fournit des voies thermiques supplémentaires, améliorant la dissipation de la chaleur pour les composants de haute puissance.

Défis en matière de fabrication:

- Forage Microvia: Requires laser drilling for 50–100 μm microvias with ±15 μm positioning accuracy

- Via Filling: Le remplissage de résine assisté par le vide garantit l'absence de bulles dans les espaces vides, avec un retrait du matériau inférieur à 2 %.

- Planéité de la surface: Post-filling, precision grinding ensures surface flatness within 5 μm for reliable soldering

- Gestion des contraintes thermiques: Filler materials must match copper’s thermal expansion coefficient to prevent cracking

Applications:

- Cartes mères de smartphones (en particulier pour les processeurs et la mémoire)

- GPU haut de gamme et cartes mères de serveurs

- Appareils miniaturisés pour l'IdO

- Matrices de LED à haute densité

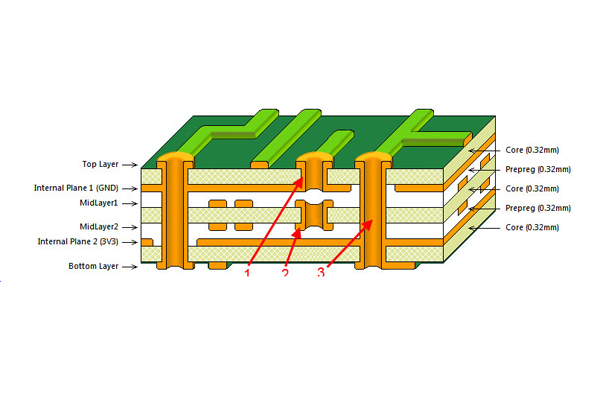

Vias aveugles et enterrés : solutions d'interconnexion en 3D

Les vias aveugles et enterrés permettent des connexions sélectives entre les couches, ce qui permet un routage tridimensionnel des circuits imprimés.

Comparaison des technologies:

| Type | Structure | Méthode de fabrication | Bénéfice principal |

|---|---|---|---|

| Via aveugle | Relie les couches extérieures aux couches intérieures | Forage au laser/à profondeur contrôlée | Réduit les effets de stub du signal |

| Enterré Via | Entièrement à l'intérieur des couches internes | Stratifié après traitement de la couche | Libère l'espace de routage de la couche externe |

Principaux défis à relever:

- Contrôle de la profondeur: Laser drilling requires precise energy/pulse control (±10 μm tolerance)

- Alignement des couches: High-precision registration systems ensure ≤25 μm misalignment

- Uniformité du placage: Pulse plating ensures even copper deposition (≥18 μm in vias)

- Test de fiabilité: Thermal cycling (-55°C to 125°C, 1000 cycles) and impedance testing

Applications industrielles:

- Modules RF pour stations de base 4G/5G

- Électronique pour l'aérospatiale et la défense

- Tableaux de commande d'équipements médicaux

- Modules de capteurs pour véhicules autonomes

Processus semi-additif modifié (mSAP) : Fabrication de circuits ultrafins

mSAP uses a “thin seed layer + selective plating” approach to achieve sub-30 μm trace/space, surpassing traditional etching limits.

Déroulement du processus:

- Préparation du substrat: Low-roughness base material (Rz < 1.5 μm)

- Dépôt d'une couche de semences: 0.3–1 μm thin copper via electroless plating

- Patterning: Laser Direct Imaging (LDI) with 5 μm resolution

- Placage: Acid copper electroplating (±2 μm thickness control)

- Enlèvement de la couche de semences: Micro-etching with <3 μm undercut

Mesures de contrôle de la qualité:

- Uniformité de la largeur de la trace : CV < ; 5% sur l'ensemble du panneau

- Variation de l'épaisseur du cuivre : <10% à l'intérieur de la carte

- Surface defects: <3 defects per m²

Produits typiques:

- PCB de type substrat pour smartphones (SLP)

- Substrats d'emballage au niveau de la plaquette

- Réseaux d'antennes à ondes millimétriques

- Modules d'interconnexion à ultra-haute densité

Applications industrielles des technologies avancées des PCB

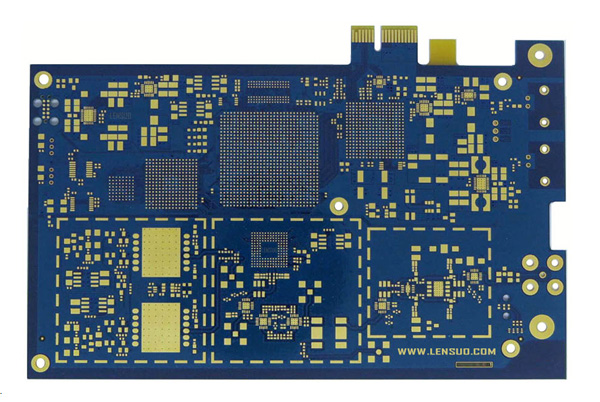

Électronique grand public

Smartphones and tablets drive advanced PCB adoption. Flagship smartphone motherboards use any-layer HDI and mSAP to achieve 20/20 μm trace/space rules, packing 14+ layers into 80×120 mm areas. Wearables employ rigid-flex PCBs, maintaining reliability at <3 mm bend radii.

Infrastructure de télécommunications

Les unités de bande de base 5G exigent des circuits imprimés à haute fréquence avec :

- Dielectric constant (Dk): 3.0±0.05 @ 10 GHz

- Tangente de perte (Df) : <0.002 @ 10 GHz

- Phase consistency: ±1.5°/inch

Ceux-ci nécessitent des systèmes de résine spécialisés et des processus d'impédance contrôlée.

Électronique automobile

Les systèmes autonomes imposent de nouvelles exigences :

- Radar PCBs: Ra < 0.3 μm surface roughness for 77 GHz

- Gestion de la batterie : Cartes à 6 couches en cuivre lourd de 2 oz (vias à rapport d'aspect de 8:1)

- Écrans :Circuits flexibles ultra-minces (>100k cycles de flexion)

Industriel & ; Équipement médical

Les contrôles industriels nécessitent :

- Circuits imprimés de puissance à 10+ couches

- -40°C to 150°C operating range

- Vibration resistance (5–500 Hz, 5 Grms)

L'imagerie médicale repose sur :

- Conception de circuits à faible bruit

- Routage analogique haute densité

- Structures de blindage EMI

Tendances futures et défis techniques

Innovations en matière de matériaux

Matériaux haute fréquence:

- Composites PTFE modifiés

- Films en polymère à cristaux liquides (LCP)

- Silice nanoporeuse

Gestion thermique:

- >5 W/mK résines à conductivité thermique

- Substrats améliorés par le graphène

- Substrats métalliques isolés

Percées dans les processus

Intégration hétérogène:

- Embedded passives (>100/cm²)

- Technologie des puces sur carte (COB)

- Circuits hybrides optoélectroniques

Fabrication de précision:

- Forage laser picoseconde/femtoseconde

- Métallisation par dépôt de couches atomiques (ALD)

- Lithographie par nano-impression

Initiatives en matière de développement durable

Procédés respectueux de l'environnement:

- Placage d'or sans cyanure

- Cuivre chimique à faible DCO

- Masques de soudure à base d'eau

Économie circulaire:

- >Récupération de 99,5 % du cuivre

- Fabrication à faible consommation d'énergie

- Substrats biodégradables

FAQ : Fabrication avancée de circuits imprimés

Q1 : Comment le via-in-pad améliore-t-il les performances thermiques ?

A1: Copper-filled vias create thermal pathways, reducing thermal resistance by >40% in 3×3 via arrays. Optimal fill density is 60–70% for thermo-mechanical reliability.

Q2 : Quels sont les avantages des trous borgnes/enfouis pour l'intégrité du signal ?

A2 : Par rapport aux trous de passage, ils :

- Shorten signal paths by 30–50%

- Reduce crosstalk by 6–8 dB @ 10 GHz

- Amélioration de l'adaptation de l'impédance (15 % de réflexion en moins)

- Cut delay by 20–30 ps/inch

Q3 : En quoi le MSAP est-il plus performant que les procédés soustractifs traditionnels ?

A3 : Les principaux avantages sont les suivants :

- Trace width accuracy: ±2 μm vs ±8 μm

- Near-vertical sidewalls (85–90° vs 45–60°)

- Finer geometries (15/15 μm vs 50/50 μm)

- Tighter impedance control (±5% vs ±10%)

Q4: How to evaluate a manufacturer’s blind/buried via capability?

A4 : Évaluer :

- Technical specs (≤50 μm microvias, ±25 μm registration)

- Données de fiabilité (cycles thermiques, analyse des sections transversales)

- Méthodes d'inspection (rayons X 3D, couverture AOI)

- Stabilité de la production (>90% de rendement à l'échelle)

Q5: What breakthroughs will shape PCB tech in 3–5 years?

A5 : Principaux développements :

- Densité plus élevée: 10/10 μm traces, hybrid mSAP/SAP

- Intégration hétérogène: Actifs/passifs intégrés, interconnexions optiques

- Matériaux avancésdiélectriques à faible perte pour les ondes millimétriques (Dk<2,5, Df<0,001)

- Fabrication intelligente: Optimisation pilotée par l'IA, jumeaux numériques

- Durabilité: > 95 % de recyclage des matériaux, 30 % de réduction de la consommation d'énergie

Alors que l'électronique continue de progresser vers plus de performance, de miniaturisation et d'efficacité, les technologies des circuits imprimés continueront de repousser les limites physiques.La compréhension de ces innovations permet aux concepteurs et aux spécialistes de l'approvisionnement de prendre des décisions éclairées, ce qui favorise le développement des produits de la prochaine génération.

Plus d'informations à ce sujet

1.Processus d'épreuvage pour la fabrication des PCB

2.Vias de circuits imprimés

3.Processus de fabrication de cartes de circuits imprimés à haute fréquence