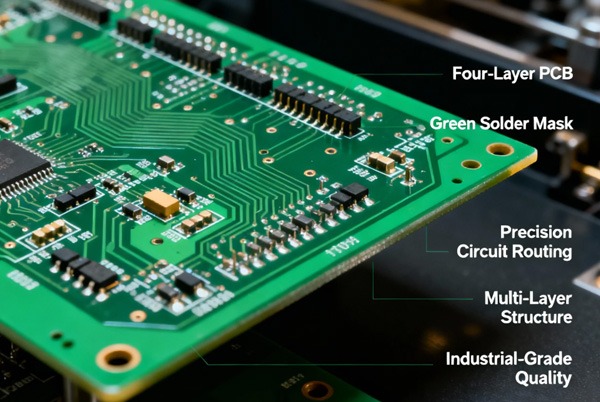

Dans le domaine de l'électronique grand public, des équipements de contrôle industriel et des systèmes numériques à haut débit, les circuits imprimés à quatre couches sont largement plébiscités pour leur compatibilité électromagnétique (CEM), leur intégrité d'alimentation et leur intégrité de signal supérieures.

Table des matières

PCB à 4 couches Structure empilée

La conception de l'empilement est à la base des performances d'une carte à 4 couches. Un empilement inapproprié peut entraîner une diaphonie des signaux, des bruits d'alimentation électrique et une non-conformité aux normes EMI.

1. Comparaison des schémas d'empilement classiques

- Schéma 1 (recommandé)

- Couche supérieure : couche de signal

- Couche 2 : Plan de masse (GND)

- Couche 3 : Plan d'alimentation (PWR)

- Couche inférieure : couche de signal

- Avantages : Le plan de masse fournit une référence solide pour les signaux de la couche supérieure. Les plans d'alimentation et de masse adjacents forment une capacité de découplage inhérente.

- Schéma 2

- Couche supérieure : couche de signal

- Couche 2 : Plan d'alimentation

- Couche 3 : Plan de masse

- Couche inférieure : couche de signal

- Scénarios applicables : Dispositifs à courant élevé (par exemple, pilotes de moteur). Notez les changements potentiels du plan de référence pour les signaux de la couche inférieure.

- Schéma 3 (à utiliser avec précaution)

- Couche supérieure : plan de masse

- Couche 2 : Couche de signal

- Couche 3 : Couche de signal

- Couche inférieure : plan de puissance

- Risques : Plan de masse incomplet, longs chemins de retour du signal. Convient principalement aux cartes à basse fréquence, dominées par les connecteurs.

2. Paramètres clés

- Épaisseur diélectrique : Recommended 0.1–0.2mm between signal and reference planes to enhance inter-layer coupling.

- Poids du cuivre : Outer layers 1oz (35μm), inner layers 0.5oz (17.5μm). Can increase to 2oz for high-current areas.

- Conception du retour en arrière : Power planes should be indented 40–80mil relative to the ground plane (20H rule) to reduce edge radiation.

Via Design

Les vias sont essentiels pour les connexions intercouches, mais ils introduisent des paramètres parasites qui affectent les signaux à haute vitesse.

1. Via la sélection du type

- Via traversants : Faible coût, adapté aux signaux standard et aux connexions électriques.

- Via aveugles/enfouis : Utilisé pour le routage d'échappement BGA haute densité, mais augmente le coût du processus.

2. Calcul des paramètres parasites

- Capacité parasite :

C ≈ 1.41ε · T · D1 / (D2 - D1)

OùTest l'épaisseur du panneau,D1est le diamètre du foret,D2est le diamètre du tampon. - Inductance parasite :

L ≈ 5.08h [ln(4h / d) + 1]

Oùhest via la longueur,dest le diamètre du foret.

3. Via les directives d'utilisation

- Pistes d'alimentation : Utilisez des vias plus grands (par exemple, 12 mil de diamètre/16 mil de perçage), placez-en plusieurs en parallèle pour réduire l'impédance.

- Signal Vias : Préférez les vias plus petits (par exemple, diamètre de 8 mil/perçage de 12 mil). Évitez le placement asymétrique dans les paires différentielles.

- Via thermiques : Placer sous les composants générateurs de chaleur (par exemple, foret de 0,3 mm, pas de 1,5 mm).

Routage de circuits imprimés

1. Procédure d'acheminement

- Commencez par vous attaquer aux zones difficiles : Commencez le routage par les zones complexes telles que les BGA et les interfaces haut débit.

- Manipulation modulaire : Acheminement par blocs fonctionnels (par exemple, microcontrôleur, mémoire, circuits analogiques) afin d'éviter les interférences croisées.

- Routage de nettoyage : Acheminez les signaux à faible vitesse en dernier, en optimisant l'utilisation des canaux grâce à l'ajustement de la largeur et de l'espacement des pistes.

2. Règles d'acheminement critiques

- Contrôle d'impédance :

- Single-ended: 50Ω. Differential pairs: 100Ω.

- Réalisez cela en ajustant la largeur de trace, l'épaisseur diélectrique et la permittivité.

- Traitement des signaux à haute vitesse :

- Donnez la priorité au routage des signaux d'horloge sur les couches internes, en référence à un plan de masse.

- Maintain length matching in differential pairs (≤5mil tolerance).

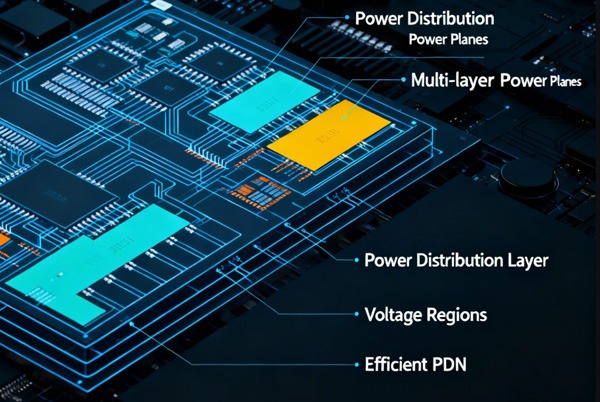

- Segmentation du plan de puissance :

- Segmentez un seul plan d'alimentation en trois régions au maximum (par exemple, 3,3 V, 5 V, 12 V).

- Use segmentation lines ≥0.5mm wide to prevent creepage issues.

Conception de l'intégrité de l'alimentation

1. Emplacement des condensateurs de découplage

- Sélection : 0.1μF ceramic capacitors (high-frequency) + 10μF tantalum capacitors (low-frequency).

- Placement : Position close to IC power pins (≤3mm). Connect directly to power/ground planes via vias.

2. Intégrité du plan de masse

- Évitez de diviser le plan de masse avec des pistes de signal afin de garantir des chemins de retour à faible impédance.

- Connect digital and analog grounds at a single point using a ferrite bead or 0Ω resistor.

Vérification de la conception et préparation de la production

1. Liste de contrôle pour la RDC

- Trace Width/Spacing: General signals ≥6/6mil, Power traces ≥12/12mil.

- Drill-to-Copper Distance: ≥8mil to prevent short circuits.

2. Simulation de l'intégrité du signal

- Utilisez des outils tels que HyperLynx ou Sigrity pour vérifier le temps de montée, l'oscillation et la continuité de l'impédance.

- Concentrez-vous sur la vérification des horloges, des signaux différentiels et des ondulations de l'alimentation électrique.

3. Sortie du fichier de production

- Fournir les fichiers Gerber (y compris les couches, le masque de soudure, le perçage), les coupons de test d'impédance et les plans d'assemblage.

Principaux enseignements en matière de conception

- Préférer le schéma d'empilement 1, garantissant un plan de masse adjacent aux couches de signaux primaires.

- Équilibrer coût et performance grâce à la conception, en utilisant des vias d'alimentation parallèles pour réduire l'impédance.

- Itinéraire suivant le principe « Difficult First » (le plus difficile en premier), en donnant la priorité aux signaux à haute vitesse sur les couches internes.

- Limiter la segmentation de l'alimentation à 3 régions, en plaçant des condensateurs de découplage à proximité des circuits intégrés.

- Valider à la fois avec la DRC et la simulation pour éviter les retouches en post-production.