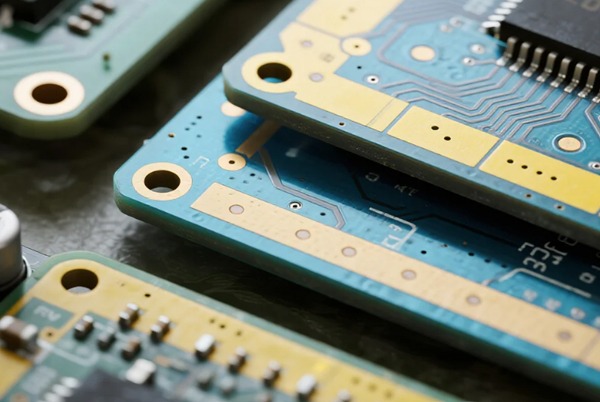

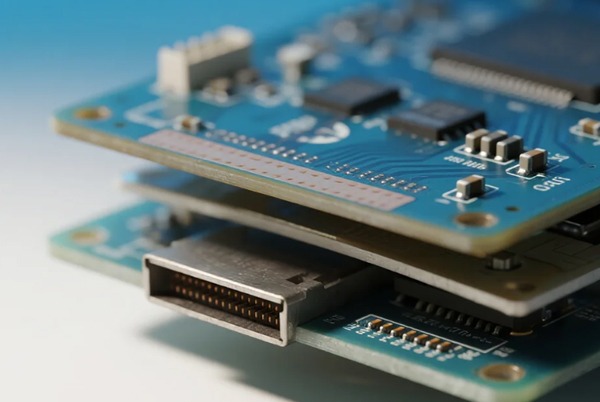

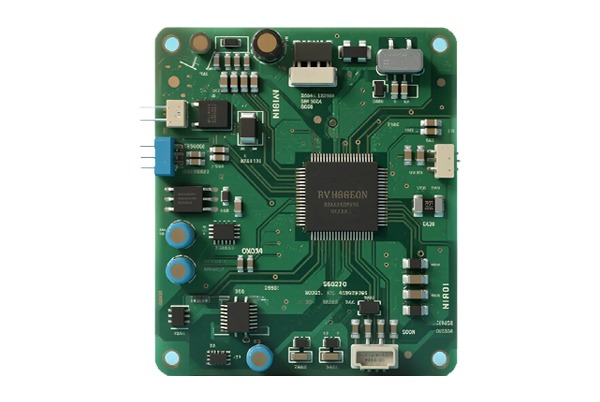

Cartes de circuits imprimés Les circuits imprimés (PCB) sont les supports centraux des appareils électroniques. Le nombre de couches qu'ils comportent a une incidence directe sur le bon fonctionnement du produit, son coût et sa fiabilité. Cet article examine les limites théoriques du nombre de couches des circuits imprimés, les aspects pratiques qui rendent leur fabrication difficile, leur comparaison en termes d'avantages et d'inconvénients selon le nombre de couches, ainsi que les aspects techniques à prendre en compte pour choisir le nombre de couches approprié. Il constitue une référence complète pour les ingénieurs en électronique et les concepteurs de produits.

Table des matières

I. Limites théoriques et contraintes pratiques de fabrication des couches de circuits imprimés

Limites théoriques de la couche

Il y a aucune limite supérieure absolue au nombre de couches dans un circuit imprimé. Grâce aux progrès réalisés dans le domaine de la microélectronique, les principaux fabricants mondiaux tels que Intel et Samsung ont réalisé la production en série de circuits imprimés avec Plus de 100 couches, principalement pour des applications spécialisées telles que les supercalculateurs, les serveurs haut de gamme et les équipements aérospatiaux.

Contraintes pratiques de fabrication

Malgré cette possibilité théorique, la production de masse pratique se heurte à plusieurs limites :

- Contraintes techniques: Les exigences en matière de précision d'alignement entre les couches augmentent de manière exponentielle à mesure que des couches sont ajoutées.

- Contraintes matériellesLes circuits imprimés à nombre élevé de couches nécessitent des matériaux hautement stables présentant de faibles coefficients de dilatation thermique.

- Contraintes budgétairesLe coût de fabrication d'un circuit imprimé à 32 couches peut être 5 à 8 fois supérieur à celui d'un circuit imprimé à 4 couches.

- Contraintes de rendement: Au-delà de 20 couches, chaque couche supplémentaire réduit le rendement d'environ 2 à 3 %.

Gammes standard de couches de production

Le tableau ci-dessous présente les répartitions typiques des couches de PCB dans différents domaines d'application :

| Champ d'application | Couches typiques | Produits représentatifs | Caractéristiques techniques |

|---|---|---|---|

| Électronique grand public | 4 à 8 couches | Smartphones, tablettes | Sensible aux coûts, contraint par l'espace |

| Équipements de communication | 8 à 16 couches | Stations de base 5G, commutateurs réseau | Exigences en matière de gestion thermique à haute fréquence et haute vitesse |

| Contrôle industriel | 6 à 14 couches | Automates programmables, cartes mères industrielles | Haute fiabilité, forte immunité aux interférences |

| Calcul haute performance | 12 à 32 couches | Serveurs, cartes accélératrices IA | Transmission à très haute densité et à grande vitesse |

| Domaines spécialisés | 32 à plus de 100 couches | Superordinateurs, équipement aérospatial | Performances extrêmes, matériaux spéciaux |

II. Analyse complète des avantages des circuits imprimés multicouches

1. Capacité d'intégration haute densité

Grâce à une conception empilée en couches, circuits imprimés multicouches améliorer considérablement la densité de câblage dans des zones limitées. Les données de test montrent que les cartes à 8 couches offrent une densité de câblage environ 60 % supérieure à celle des cartes à 4 couches, tandis que les cartes à 16 couches peuvent améliorer la densité de plus de 120 %.

2. Excellente intégrité du signal

Grâce à une conception adéquate de l'empilement et au contrôle de l'impédance, les circuits imprimés multicouches garantissent efficacement la qualité de la transmission des signaux à haut débit :

- Cartes à 4 couchesRéduisez l'atténuation du signal de plus de 40 % par rapport aux cartes double face à une fréquence de 1 GHz.

- Cartes à 8 couches: Prise en charge d'interfaces haut débit telles que PCIe 4.0 avec des débits de transmission pouvant atteindre 16 GT/s.

- Cartes à plus de 16 couches: Support 56Gbps and above high-speed serial transmission with bit error rates below 10⁻¹²

3. Compatibilité électromagnétique (CEM) supérieure

Les circuits imprimés multicouches offrent un blindage électromagnétique naturel grâce à une conception complète des plans de masse et d'alimentation :

- Lorsque la couverture du plan de masse est supérieure à 85 %, le rayonnement électromagnétique peut être réduit de 12 à 15 dB.

- La séparation des couches d'alimentation/masse des couches de signal réduit les interférences électromagnétiques intercouches de plus de 20 dB.

4. Performances thermiques efficaces

- Dedicated thermal layer designs can reduce chip junction temperature by over 18℃

- Aluminum substrates achieve thermal conductivity coefficients of 2.2W/m·K, 3-5 times better than traditional FR-4 material

5. Flexibilité de conception et optimisation de l'espace

- 10-layer HDI boards can reduce smartphone motherboard size to 5cm×5cm, saving 70% space compared to traditional solutions

- L'espace de câblage tridimensionnel permet des conceptions de circuits plus complexes.

III. Défis et limites des circuits imprimés multicouches

Analyse des coûts de fabrication

Le nombre de couches d'un circuit imprimé et son coût suivent une relation de croissance non linéaire :

| Couches | Coût relatif | Principaux facteurs de coût |

|---|---|---|

| 2 couches | 1.0x | Matériau de base, processus simples |

| 4 couches | 1,8-2,5x | Augmentation des cycles de laminage, exigences d'alignement plus élevées |

| 6 couches | 3-4 fois | Complexité accrue du forage, réduction du rendement |

| 8 couches | 4 à 6 fois | Augmentation des coûts des matériaux, complexité accrue des processus |

| 16 couches | 8-12x | Exigences particulières en matière d'équipement, augmentation significative des coûts des essais |

Cycles de production prolongés

La fabrication de circuits imprimés multicouches nécessite plusieurs processus de laminage, de perçage et de placage :

- Délai standard pour les cartes à 4 couches : 5 à 7 jours

- Délai standard pour les cartes à 8 couches : 10 à 14 jours

- Délai standard pour une carte à 16 couches : 15 à 25 jours

- Délai standard pour une carte à 32 couches : 30 à 45 jours

Défis liés aux tests et aux réparations

- Les circuits imprimés à nombre élevé de couches nécessitent plusieurs méthodes de test, notamment le test à sonde mobile et l'inspection par rayons X.

- Localisation interne difficile des défauts, taux de réussite généralement inférieur à 30 % pour les réparations de boîtiers BGA.

- Les coûts liés aux essais peuvent représenter 15 à 20 % du coût total de fabrication.

IV. Méthodologie de sélection des couches de circuits imprimés et directives de conception

Facteurs déterminants pour la couche clé

- Complexité fonctionnelle: Le nombre de lignes de signal est un indicateur clé.

- <50 lignes : possibilité d'envisager des cartes double face

- 50 à 200 lignes : cartes à 4 couches recommandées

- >200 lignes : nécessite 6 couches ou plus

- Exigences relatives à la fréquence du signal

- <50 MHz : les cartes double face peuvent suffire

- 50 MHz-100 MHz : cartes à 4 couches recommandées

- >100 MHz : doit utiliser au moins 6 couches

- Niveaux GHz : nécessitent plus de 8 couches avec une conception professionnelle

- Exigences en matière de câblage des boîtiers BGA

- Pas de 0,65 mm : des cartes à 4 couches peuvent suffire

- Pas de 0,4 mm : doit utiliser au moins 6 couches

- Pour chaque réduction de pas de 0,1 mm, il est recommandé d'ajouter 1 à 2 couches de routage.

Conception optimisée de la structure empilée

Structures empilées recommandées pour différents nombres de couches :

Structure à 4 couches préférée:

Haut (signal) - Couche de masse - Couche d'alimentation - Bas (signal)Structure optimisée à 6 couches:

Haut (signal) - Couche de masse - Couche de signal - Couche de signal - Couche d'alimentation - Bas (signal)Structure avancée à 8 couches:

Couche de signal - Couche de masse - Couche de signal - Couche d'alimentation - Couche de masse - Couche de signal - Couche d'alimentation - Couche de signalV. Technologies clés pour augmenter le nombre de couches des circuits imprimés

Technologies avancées d'interconnexion

- Technologie de perçage au laser

- UV laser enables 25μm microvia processing

- Precision up to ±5μm, supporting blind and buried via fabrication

- Technologie d'interconnexion de couches quelconques (ALIVH)

- Réalise des connexions verticales entre deux couches quelconques grâce à des vias empilés.

- Améliore la densité de connexion intercouche de 40 %.

- Combinaisons de procédés pour vias borgnes/enterrés

- Via aveugles : connexions entre la surface et la couche interne, diamètre de 0,05 à 0,3 mm

- Vias enterrés : connexions entre couches internes, entièrement dissimulées

Innovations en matière de matériaux

- Technologie hybride haute fréquence

- Combine des matériaux haute fréquence (par exemple, Rogers) avec du FR-4.

- Utilise des matériaux haute fréquence pour les couches de signaux critiques, du FR-4 économique pour les autres couches.

- Matériaux diélectriques à très faible perte

- Rogers RO4835 : perte diélectrique de seulement 0,0035 à 10 GHz

- Atténuation du signal de seulement 0,3 % sur une transmission de 1 mètre

Percées dans les processus

- Technologie de stratification par étapes

- Utilise des structures de stratification symétriques pour contrôler le gauchissement.

- Interlayer alignment error ≤5μm

- Technologie de remplissage par placage

- Le placage par impulsions permet d'obtenir un remplissage sans vide.

- Blindage via rapport d'aspect de placage 0,8:1

VI. Cas d'application et tendances technologiques

Cas d'application réussis

| Produit d'application | Couches | Caractéristiques techniques | Amélioration des performances |

|---|---|---|---|

| Station de base 5G Huawei | 24 couches | Hybrides haute fréquence + perçage laser | Réduction de 80 % du retard du signal |

| Ordinateur automobile Tesla | 12 couches | Matériaux haute température + refroidissement amélioré | Operating temperature -40℃~125℃ |

| Carte mère iPhone | 10 couches | N'importe quelle couche HDI | Réduction de volume de 40 % |

| Carte accélératrice IA NVIDIA | 16 couches | Matériaux à très faible perte | Débit de transmission de 112 Gbit/s |

Tendances futures du développement

- Augmentation continue de la couche: L'électronique grand public évolue vers 12 à 16 couches, tandis que l'informatique haut de gamme tend vers plus de 50 couches.

- Innovation matérielle: Développement de nouveaux matériaux avec une constante diélectrique < 3,0 et un facteur de perte < 0,002.

- Intégration: Intégration de composants passifs, d'antennes, etc., à l'intérieur de circuits imprimés

- Gestion thermique: Developing thermal materials with conductivity >5W/m·K

Conclusion

Le choix du nombre de couches d'un circuit imprimé est une tâche d'ingénierie système complexe qui nécessite de trouver un équilibre entre performances, coût, fiabilité et faisabilité de fabrication. Des simples cartes double face aux cartes complexes dépassant 32 couches, chaque option présente des scénarios d'application et des exigences techniques spécifiques. Avec les progrès technologiques tels que la 5G, l'intelligence artificielle et l'Internet des objets, la demande en circuits imprimés à couches multiples continuera de croître, poussant la technologie des circuits imprimés vers une densité, des performances et une fiabilité accrues.