Un circuit imprimé quadri-couche est un circuit imprimé multicouche qui se compose généralement d'une couche de signal interne, d'une couche d'alimentation interne, d'une couche de signal externe et d'une couche de montage de la pièce externe. Par rapport aux circuits imprimés simple face et double face, les circuits imprimés quadri-couches offrent une meilleure intégration, une taille plus petite et des performances plus stables, car ils peuvent faire passer l'énergie dans la couche d'alimentation interne (une couche que l'on ne trouve pas sur les circuits imprimés ordinaires), réduisant ainsi les interférences et le bruit et garantissant la stabilité du circuit.

Table des matières

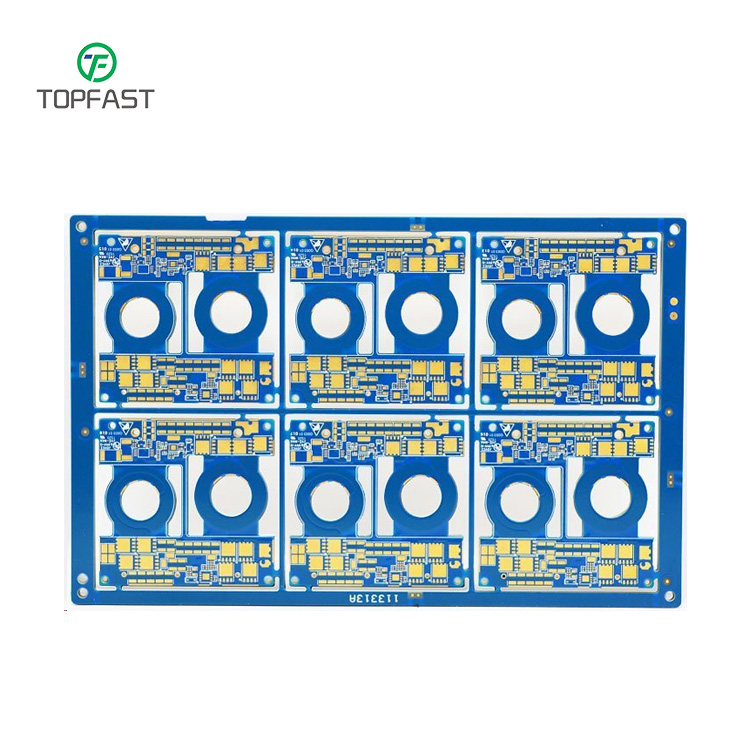

Spécifications techniques de Cartes de circuits imprimés à 4 couches

Structure de base

Un circuit imprimé à 4 couches adopte la configuration classique “signal-alimentation-masse-signal” ; empilage :

- Couche supérieure: Montage des composants et routage en surface

- Couche intérieure 1: Couche de transmission des signaux (priorité aux signaux à haute fréquence)

- Couche intérieure 2: Plan de puissance (Power Plane)

- Couche inférieure: Couche de signal et surface de soudure

Comparaison des avantages fondamentaux

| Mesure de la performance | PCB double couche | PCB à 4 couches | Amélioration |

|---|---|---|---|

| Densité d'acheminement | 2-4 lignes/cm | 8-12 lignes/cm | 300% |

| Intégrité du signal | 60-80Ω impedance variation | ±5% impedance control | 5 fois mieux |

| Bruit de puissance | 50-100mV | 10mV | 90% de réduction |

| Performances EMC | Nécessite un blindage supplémentaire | Couches de blindage intégrées | Conforme à la classe B |

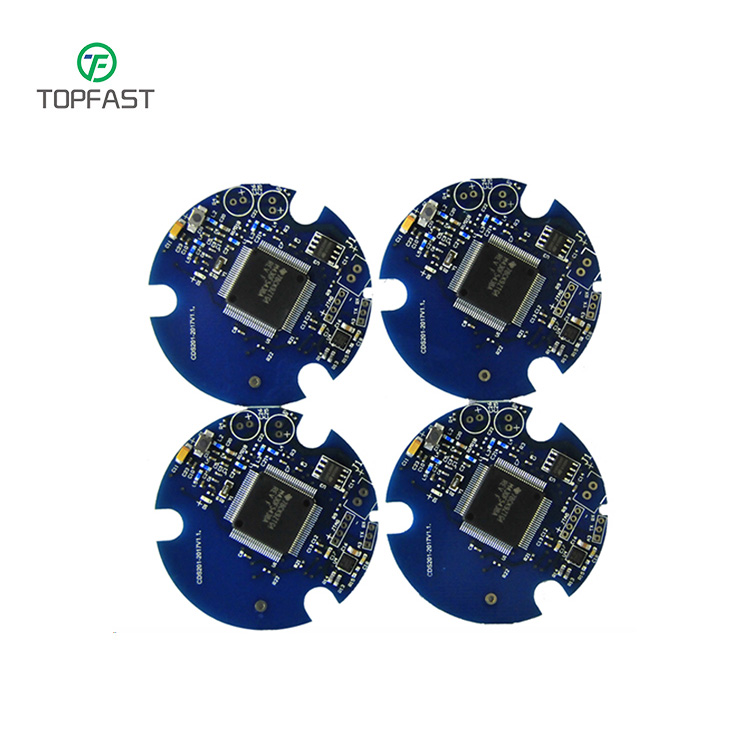

Applications typiques

- Circuits numériques à grande vitesse

- Caractéristiques : Fréquences d'horloge supérieures à 100 MHz

- Mise en œuvre :Trajets de retour complets via les plans de masse intérieurs

- Exemple :Cartes de processeurs ARM (HDI à 6 couches avec vias aveugles/enfouis)

- Systèmes mixtes analogiques

- Solution : Alimentations numériques/analogiques séparées

- Disposition :Signaux analogiques sur la couche supérieure + signaux numériques sur les couches intérieures

- Performance :Diaphonie < ; -60dB @1GHz

- Conception de l'électronique de puissance

- Configuration : plan de puissance en cuivre de 2 oz d'épaisseur

- Capability: Current density up to 10A/mm²

- Gestion thermique : Réseau de via pour la dissipation de la chaleur

Points clés de la fabrication

- Contrôle du pelliculage

- Dielectric thickness: 0.2mm ±5%

- Options de poids du cuivre : 1oz / 2oz

- Alignment accuracy: ≤50μm

- Via Design

- Trou débouchant : 0,3 mm/0,6 mm (diamètre du trou/plaque)

- Vias aveugles : L1-L2 ou L3-L4

- Vias enterrés :L2-L3 (nécessite un perçage au laser)

- Contrôle de l'impédance

- Microstrip: 50Ω ±10% (outer layers)

- Stripline: 100Ω differential (inner layers)

- Vérification :Essais TDR (Time Domain Reflectometry)

Lignes directrices de sélection

- Cas d'utilisation recommandés

- Operating frequency ≥50MHz

- Component count ≥100

- BGA packages (pitch ≤0.8mm)

- Nécessite 4+ domaines de puissance

- Optimisation des coûts

- Standard FR4 material (TG≥130℃)

- Trace/espace minimum : 4mil/4mil

- Éviter les vias aveugles/enfouis

Note: Les circuits imprimés modernes à 4 couches supportent un tracé/espace de 3 millimètres avec des microvias de 0,25 mm, ce qui permet d'obtenir une densité de routage comparable à celle des circuits à 6 couches. Selon les normes IPC-2221B, les circuits imprimés à 4 couches ont une durée de vie de 10 ans (applications industrielles).

Processus de fabrication complet des cartes de circuits imprimés à 4 couches

Phase d'ingénierie de conception

- Vérification de la conception par l'EDA

- Outils professionnels : Cadence Allegro/Mentor Xpedition

- Analyse de l'intégrité du signal (HyperLynx)

- Sortie : Fichiers de production au format Gerber 274X

- Paramètres clés :

✓ Minimum trace/space: 3/3mil

✓ Impedance control: ±10%

✓ Via count: ≥2000/m²

Préparation des matériaux & ; Traitement

- Sélection de stratifiés plaqués cuivre

- Standard FR-4 (TG150)

- Options d'épaisseur du cuivre : 1/2oz réglable

- Dimensional tolerance: ±0.1mm

- Perçage de précision

- Équipement :Machine de forage CNC à 6 axes

- Précision :

✓ Hole position deviation: ≤25μm

✓ Hole diameter tolerance: ±50μm - Paramètres typiques :

✓ Spindle speed: 150krpm

✓ Panel stack thickness: ≤2.4mm

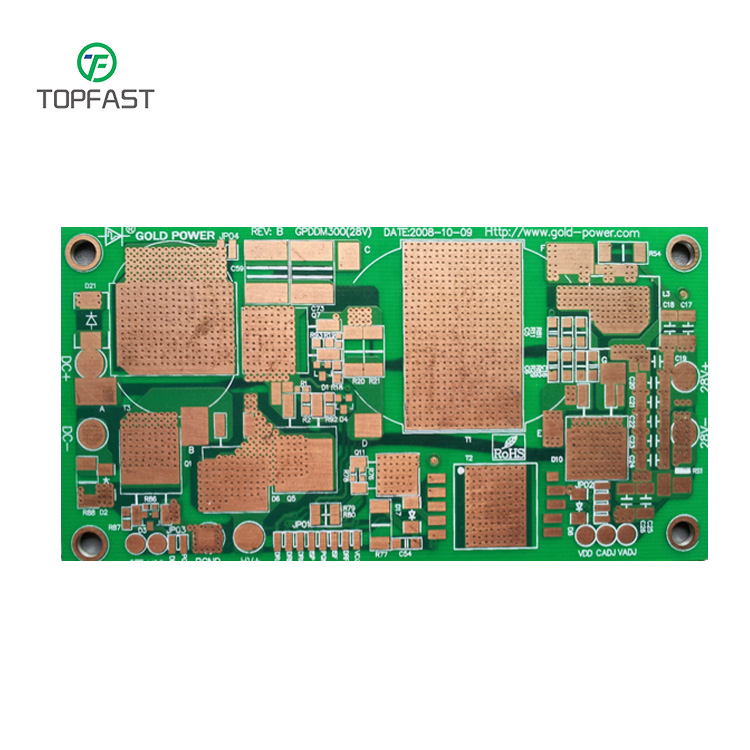

Procédé de laminage multicouche

- Empilement de couches

| Couche | Désignation | Épaisseur (mm) | Poids du cuivre | Fonction principale |

|---|---|---|---|---|

| Top | Couche de signal (L1) | 0.035 ±0.005 | 1 oz | Placement des composants & ; routage |

| Intérieur | Plan d'alimentation (L2) | 0.50 ±0.05 | 2 oz | Distribution d'énergie & ; découplage |

| Intérieur | Plan de masse (L3) | 0.50 ±0.05 | 2 oz | Chemin de retour du signal & ; blindage EMI |

| Le fond | Couche signal (L4) | 0.035 ±0.005 | 1 oz | Routage secondaire & ; soudure |

2. Paramètres de laminage

- Temperature: 180±5℃

- Pressure: 300±50psi

- Duration: 90±10 minutes

- Vacuum level: ≤10mbar

Technologie de transfert de modèles

- Exposition LDI

- Resolution: 20μm

- Alignment accuracy: ±15μm

- Capacité : 50 panneaux/heure

- Gravure sur circuit

- Etch factor: ≥3:1

- Undercut control: ≤10%

- Copper thickness uniformity: ±5%

Placage & ; Finitions de surface

- Métallisation des trous

- Electroless copper: 0.5-1μm

- Electroplated copper: 25±5μm

- Hole wall pull strength: ≥1.0N/mm

2. Options de finition de surface

| Finition de la surface | Spécifications techniques | Gamme d'épaisseur | Caractéristiques principales | Applications recommandées | Durée de conservation | Norme IPC |

|---|---|---|---|---|---|---|

| ENIG (nickel chimique, immersion dans l'or) | Ni: 3-5μm Au: 0.05-0.1μm | Ni: 120-200μin Au: 2-4μin | – ; Excellente planéité – ; Bonne soudabilité – ; Fil d'aluminium collable | – ; Boîtiers BGA – ; Composants à pas fin (<0.5mm) – ; Connecteurs | 12 mois | IPC-4552 |

| OSP (conservateur de soudabilité organique) | 0.2-0.5μm | 8-20μin | – ; Rentabilité – ; Compatible sans plomb – ; Processus simple | – ; Electronique grand public – ; Général Assemblage SMT – ; Production en grande quantité | 6 mois | IPC-4555 |

| Étain d'immersion | 0.8-1.2μm | 30-50μin | – ; Excellente soudabilité – ; Surface plane – ; Convient pour le press-fit | – ; Électronique automobile – ; Applications à haute fiabilité – ; Circuits RF/micro-ondes | 9 mois | IPC-4554 |

Système de vérification de la qualité

- Essais électriques

- Test de la sonde volante :

✓ Test speed: 200 points/sec

✓ Minimum pitch: 4 mil - Test d'impédance :

✓ TDR resolution: 5ps

✓ Test points: ≥5/impedance line

- Inspection visuelle

- AOI :

✓ Resolution: 10μm

✓ Defect detection rate: ≥99.7% - Analyse de la microsection :

✓ Sampling frequency: 1/100m²

✓ Inspection items: 20+ parameters

Contrôles de processus spéciaux

- Contrôle de l'impédance

- Microstrip: 50Ω±5%

- Stripline: 100Ω±7%

- Differential pairs: ±8%

- Gestion thermique

- Vias thermiques : 0,3 mm de diamètre

- Distribution density: 25/cm²

- Option d'épaisseur de cuivre : 2oz

Remarque : Ce procédé est conforme aux normes IPC-6012 Classe 3, et convient aux applications à haute fiabilité telles que l'électronique automobile et les commandes industrielles. La fabrication moderne de circuits imprimés à 4 couches permet d'obtenir un tracé de 3 millimètres par espace grâce à la technologie de perçage au laser, ce qui offre une densité de routage comparable à celle de l'IDH.

Conception et analyse des avantages d'une structure d'empilage de circuits imprimés à 4 couches

Structure de base et configuration des couches

Une carte de circuit imprimé (PCB) à 4 couches adopte une structure composite multicouche, composée principalement des couches fonctionnelles suivantes :

- Couches de signaux: Y compris les Couche supérieure and Couche inférieureresponsable de l'acheminement des différents signaux.

- Couche d'alimentation (plan d'alimentation): Fournit une distribution stable de l'énergie aux composants du circuit.

- Couche de sol (plan de sol): Établit le potentiel de référence du système et fournit un blindage électromagnétique.

Deux configurations d'empilage sont couramment utilisées :

Option A: Top Layer → Power Layer → Ground Layer → Bottom Layer

- Caractéristiques: Couplage étroit entre les plans de puissance et de masse, formant une capacité planaire effective, particulièrement adaptée à la conception de circuits à haute fréquence.

Option B: Top Layer → Ground Layer → Power Layer → Bottom Layer - Caractéristiques: La couche de masse fournit un blindage étroit pour les couches de signaux, réduisant de manière significative la diaphonie entre les signaux à grande vitesse.

Avantages techniques en détail

1. Optimisation des performances électriques

(1) Assurance de l'intégrité du signal

- Les chemins de retour à faible impédance via les plans de masse réduisent l'inductance de la boucle du signal.

- Planar capacitance effect (typically ~100pF/cm²) provides power decoupling and suppresses power noise.

- Strict impedance control (within ±10% tolerance) minimizes signal reflections.

(2) Compatibilité électromagnétique (CEM) améliorée - Forme une cage de Faraday complète, réduisant les interférences rayonnées jusqu'à 20dB.

- L'empilage symétrique équilibre la distribution du champ électromagnétique, réduisant ainsi le bruit en mode commun.

- Le découplage des couches de signal et d'alimentation réduit la diaphonie en 30-40%.

2.Amélioration de la flexibilité de la conception

- Augmentation de plus de 200 dans les canaux de routage par rapport aux cartes à deux couches.

- Soutien interconnexion à haute densité (HDI) dessins avec trace/espace jusqu'à 3/3 mil.

- Les signaux sensibles peuvent être acheminés sur les couches internes pour un blindage EMI inhérent.

3.Fiabilité mécanique accrue

- Collage des couches intermédiaires du FR-4 offre une excellente résistance mécanique.

- CTE (coefficient de dilatation thermique) assorti réduit les contraintes thermiques.

- Amélioration de plus de 50 de résistance à la flexion par rapport aux structures à deux couches.

Recommandations pour l'application

Principales considérations en matière de conception :

- Circuits numériques à grande vitesse → Prefer Option A.

- Systèmes à signaux mixtes → Recommend Option B.

- Applications critiques pour l'intégrité de l'alimentation → Ensure plane spacing ≤ 0.2mm.

- Signaux critiques → Use routage de stripline pour une meilleure immunité au bruit.

Applications typiques:

- Matériel de communication (stations de base 5G, routeurs)

- Systèmes de contrôle industriel

- Électronique automobile

- Électronique grand public haut de gamme

Note: Les conceptions actuelles doivent intégrer adaptation d'impédance et optimisation de l'épaisseur de l'empilage, avec Outils de simulation SI/PI recommandé pour la pré-vérification.

Exigences en matière de processus de fabrication pour la structure empilée de circuits imprimés à 4 couches

1. Technologies critiques du processus de lamination

(1) Contrôle des paramètres du processus

- Plage de température: 180-200°C (material-dependent)

- Pression requise: Pression uniforme de 300-500 psi

- Temps de séchageDurée : 90-120 minutes

(2) Points de contrôle de la qualité

- Précision de l'alignement couche par couche: ≤50μm

- Force d'adhérence: ≥1.2 N/mm²

- Taux d'annulation: <1% (inspection aux rayons X)

2.Perçage de précision & ; Processus de placage

(1) Exigences en matière de forage

- Précision du positionnement: ±25μm

- Tolérance sur le diamètre du trou: ±50μm

- Taille minimale du trou: 0,15 mm (perçage mécanique)

(2) Spécifications de la clé de placage

- Uniformité de l'épaisseur du cuivre: ±5μm

- Trou Paroi Épaisseur du cuivre: ≥25μm

- Adhésion au placage: Passes thermal stress test (288°C, 10s)

3.Procédés de finition de surface

(1) Normes relatives au masque de soudure

- Contrôle de l'épaisseur: 15-25μm

- Résolution: ≤50μm line width

- Résistance à la chaleur: Réussit 3 cycles de refusion

(2) Exigences techniques en matière de sérigraphie

- Précision des caractères: ±75μm

- Largeur minimale des lignes: 0,15 mm

- Adhésion: Pas de décollement lors du test du ruban 3M

4.Validation des processus et essais

(1) Éléments du test de fiabilité

- Essai de cyclage thermique: -40°C to +125°C, 1000 cycles

- Test d'humidité: 85°C/85% RH, 1000 hours

- Essai de vibration mécanique20G, 3 axes (2 heures chacun)

(2) Essais de performance électrique

- Test d'impédance: ±10% tolerance

- Résistance de l'isolation: ≥100MΩ

- Test haute tension: 500V DC, 60s

5.Optimisation des processus de fabrication

(1) Applications des matériaux avancés

- Substrats à faibles pertes (Dk≤3.5, Df≤0.005)

- Matériaux à haute teneur en Tg (Tg≥170°C)

- Matériaux écologiques sans halogène

(2) Technologies de traitement de pointe

- Perçage au laser (hole size ≤0.1mm)

- Interconnexion HDI toute couche

- Processus semi-additif modifié (mSAP) pour les traces fines

Recommandations pour l'application :

- Circuits haute fréquence → Use low-loss material lamination

- Conceptions à haute densité → Laser drilling + via filling plating

- Électronique automobile → Must comply with AEC-Q100 normes

- Militaire/Aérospatiale → Recommended triple laminage pour une fiabilité accrue

Remarque : La fabrication devrait suivre IPC-6012 normes, avec les points de contrôle des processus critiques (CP) pour la surveillance de l'ensemble du processus.

Méthodes d'optimisation pour le processus de fabrication de circuits imprimés à 4 couches

1. Stratégies d'optimisation de la conception

(1) Optimisation de la structure de l'empilage

- Architecture recommandée “S-G-P-S” ; (Signal-Ground-Power-Signal)

- Contrôle des paramètres clés :

- Dielectric thickness tolerance ±10%

- Impedance matching error ≤±5%

- Layer-to-layer alignment deviation ≤50μm

(2) Optimisation de la conception des itinéraires

- Traitement des signaux à grande vitesse :

- Priorité donnée à l'acheminement de la couche interne de stripline

- L'espacement des paires différentielles suit le principe 3W

- Critical signals implement length matching (±50ps)

- Conception de l'intégrité de l'alimentation :

- La segmentation des plans suit la règle des 20H

- Decoupling capacitor density: 0.1μF/cm²

2.Contrôles clés du processus de production

(1) Normes de sélection des matériaux

- Applications à haute fréquence :

- Rogers RO4003C (Dk=3,38, Df=0,0027)

- Dielectric thickness tolerance ±5μm

- Applications standard :

- Matériau FR-4 TG170

- Copper foil roughness Rz≤3μm

(2) Contrôles critiques des processus

- Procédé de laminage :

- Vacuum hot press molding (180℃/400psi)

- Interlayer resin flow control ±5%

- Métallisation des trous :

- Laser drilling taper ≤5°

- Hole copper thickness ≥25μm (CPK≥1.33)

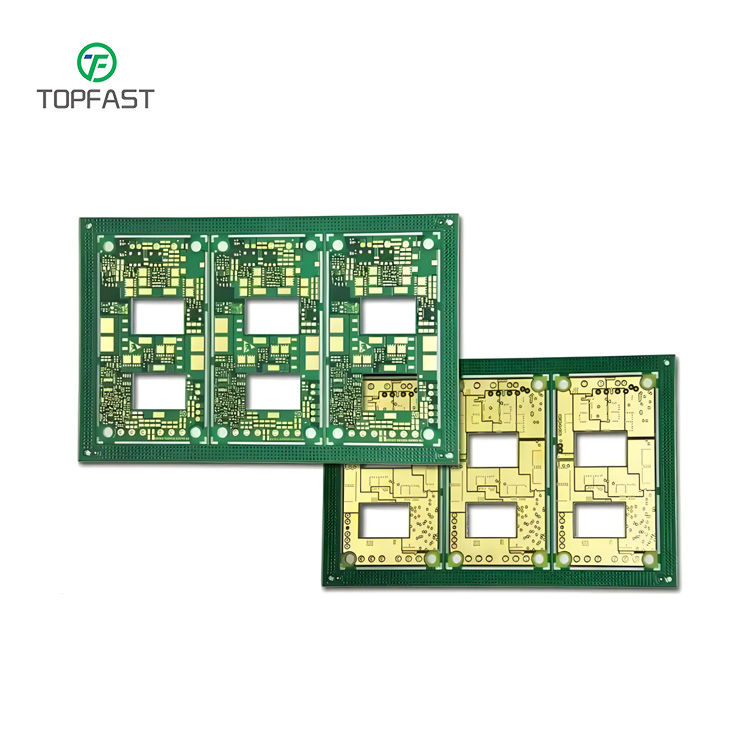

3.Solutions d'optimisation des coûts

(1) Amélioration de l'efficacité de la production

- Conception du panel :

- Standard size 406mm×508mm utilization ≥85%

- Optimisation de la largeur du cadre de traitement à 3 mm

- Simplification des processus :

- Adoption de la technologie d'imagerie directe LDI

- Achieve solder mask bridge ≤50μm

(2) Collaboration au niveau de la chaîne d'approvisionnement

- Normalisation des matériaux :

- Spécifications de la carte unifiée (0,2/0,5/1,0 mm)

- Mise en place d'une gestion des stocks VMI

- Normalisation des processus :

- Élaboration de spécifications de processus universelles (couvrant 90 % des produits)

- Établissement d'une liste de fournisseurs qualifiés

Évaluation de l'efficacité de la mise en œuvre :

- Amélioration de la performance électrique :

- L'intégrité du signal est améliorée de 30 %.

- Réduction de 40 % du bruit de fond

- Optimisation des coûts de production :

- L'utilisation des matériaux a augmenté de 15 %.

- Réduction du cycle de production de 20

- Fiabilité de la qualité :

- Le rendement au premier passage est passé à 98,5 %.

- MTBF étendu à 100 000 heures

Note : Les outils d'analyse DFM sont recommandés pour la pré-vérification, avec l'établissement d'une base de données de paramètres de processus pour l'optimisation continue. Les produits à haute fréquence nécessitent une vérification supplémentaire de la simulation du champ électromagnétique en 3D.