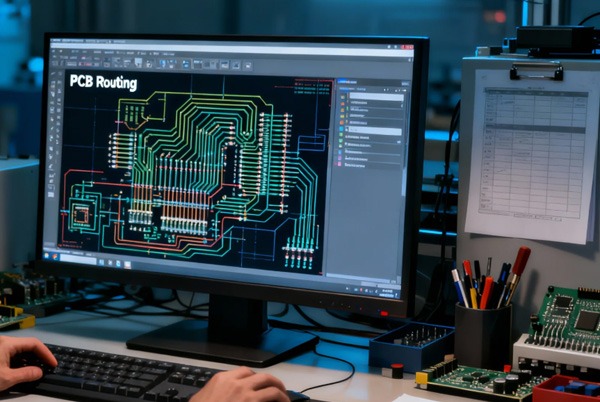

In projeto de PCB de alta velocidadeA integridade do sinal é um dos principais desafios enfrentados pelos engenheiros. O princípio 3W, como estratégia eficaz de roteamento, pode reduzir significativamente os problemas de interferência e garantir o funcionamento estável do circuito.

Índice

A definição central do princípio das 3W

O que é a regra dos 3W?

A regra dos 3W é uma diretriz fundamental no roteamento de PCB que exige o espaçamento entre os centros dos traços de sinal adjacentes não deve ser inferior a 3 vezes a largura do traço. Specifically, if the signal trace width is W, then the center distance between two parallel traces should satisfy L ≥ 3W, resulting in an edge-to-edge spacing of 2W.

Base física da regra dos 3W

Crosstalk is primarily caused by parasitic capacitance and mutual inductance between traces. According to the capacitance formula C = εS/d, where:

- C representa a capacitância parasítica entre os traços

- ε is the dielectric constant

- S é a área relativa do condutor

- d é a distância entre os condutores

Aumentando o espaçamento entre traços (d) reduz diretamente a capacitância parasitária, diminuindo assim a interferência. A intensidade do acoplamento do campo elétrico diminui exponencialmente com o aumento da distância. Experiências comprovam que um espaçamento de 3 vezes a largura do traço pode isolar mais de 70% da interferência do campo elétrico, enquanto um espaçamento de 10 vezes pode reduzir a interferência em até 98%.

Aplicação prática e limitações da regra dos 3W

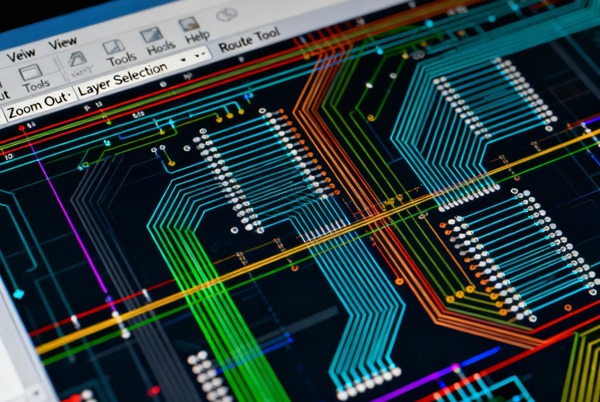

Cenários de aplicativos

A regra dos 3W aplica-se principalmente aos seguintes traços de sinal sensíveis:

- Sinais de relógio de alta frequência

- Barramentos de dados de alta velocidade (por exemplo, DDR, PCIe)

- Par de sinais diferenciais

- Linhas de sinal de vídeo e áudio

- Linhas de reinicialização e controle do sistema

Avaliação da eficácia e limitações

- Eficácia: O espaçamento de 3W reduz a interferência em aproximadamente 70%, enquanto o espaçamento de 10W pode reduzir quase 98%.

- LimitaçõesA regra dos 3W é válida em condições de impedância característica de 50 ohms, e sua eficácia é significativamente influenciada pela estrutura de empilhamento:

- Placa de quatro camadas (espaçamento de 5-10 mil entre o traço e o plano de referência): 3 W geralmente é suficiente

- Placa de duas camadas (espaçamento de 45-55 mil entre o traço e o plano de referência): 3 W podem ser insuficientes, e pode ser necessário aumentar o espaçamento.

Estratégias de design complementares à regra das 3W

Traços de guarda

Para traços de sinal particularmente sensíveis, projeto de rastreamento de guarda can be employed—placing ground traces on both sides of the signal trace and connecting them to the reference plane via ground vias. This method effectively absorbs crosstalk signals and may allow for some relaxation of the 3W spacing requirement in certain cases.

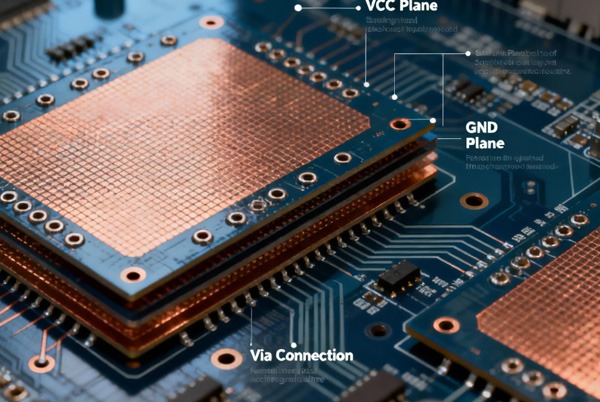

Combinação com a Regra 20H

Para resolver os problemas de radiação nas bordas do plano de alimentação, o Regra das 20H can be applied—insetting the power plane by 20 times the dielectric thickness can suppress 70% of edge flux leakage, working synergistically with the 3W rule to reduce overall EMI.

Projeto de sinal diferencial

Para pares diferenciais de alta velocidade, além do controle de espaçamento, certifique-se de:

- Correspondência rigorosa do comprimento (normalmente desvio <5 mil)

- Controle consistente da impedância

- Abordagem de roteamento simétrico

Aplicação flexível e ajuste da regra dos 3W

Ajuste dinâmico do espaçamento

3W é um valor empírico e não uma regra absoluta. O espaçamento real deve ser ajustado com base em:

- Taxa de sinal: Signals ≥500MHz may require 4W or 5W spacing

- Material dielétrico: Constantes dielétricas diferentes afetam os níveis de interferência

- Requisitos de impedância: A correspondência específica da impedância pode influenciar o espaçamento ideal.

Consideração da Regra 3H

Quando a camada de traço estiver distante do plano de referência, considere o Regra das 3 horas—trace spacing should not be less than 3 times the distance from the trace layer to the reference plane. This focuses more on electric field coupling control, complementing the 3W rule (which emphasizes magnetic field coupling).

Verificação e simulação do projeto

Necessidade da simulação

Após a conclusão do roteamento, é essencial realizar uma verificação por meio de ferramentas de simulação profissionais:

- Análise de interferência

- Verificação da integridade do sinal

- Avaliação da continuidade da impedância

Caso prático de teste

Um caso de projeto de roteador 5G mostrou que, ao aumentar o espaçamento entre os sinais de RF e Ethernet de 0,8 mm para um equivalente a 1 mm, combinado com isolamento de cobre aterrado, o projeto passou com sucesso nos padrões de teste de EMI.

Problemas e soluções comuns

A regra dos 3W se aplica a todos os traços?

Não. A regra 3W visa principalmente o roteamento de longa distância de sinais de alta velocidade. Para sinais de baixa velocidade ou traços de curta distância, os requisitos podem ser adequadamente flexibilizados para melhorar a densidade do roteamento.

Como chegar a um acordo quando o espaço é limitado?

Quando o espaço da placa for limitado, considere:

- Reduzindo o espaçamento para sinais não críticos

- Usando traços de proteção em vez de aumentar o espaçamento

- Otimização da estrutura de empilhamento para reduzir a distância entre os traços e o plano de referência

Equilibrando a regra dos 3W e o controle de impedância

Em áreas com controle rigoroso de impedância, pode ser necessário ajustar o espaçamento de 3 W para atender aos requisitos de impedância. Simulações devem determinar a solução de compromisso ideal nesses casos.

Conclusão

O princípio 3W é uma ferramenta vital no Projeto de PCB caixa de ferramentas do engenheiro, mas não é uma solução universal. Um projeto de roteamento bem-sucedido requer uma consideração abrangente das características do sinal, da estrutura da camada da placa, dos requisitos de impedância e dos objetivos de EMC, integrando o princípio 3W com outras estratégias de projeto, como planos de aterramento, a regra 20H e o projeto de pares diferenciais. Somente por meio de um processo iterativo de análise teórica, verificação de simulação e testes práticos é possível alcançar um equilíbrio ideal entre integridade do sinal, desempenho de EMC e custos de fabricação.