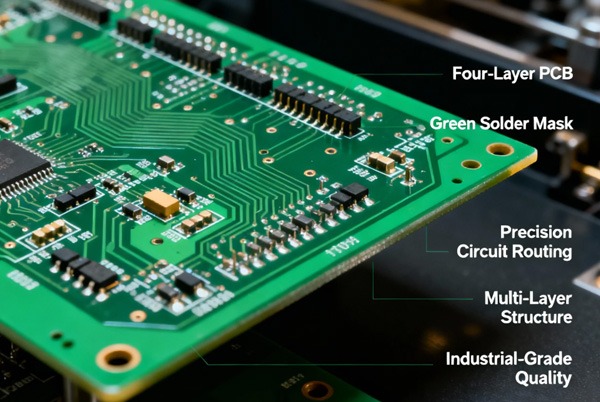

Em eletrônicos de consumo, equipamentos de controle industrial e sistemas digitais de alta velocidade, as placas de circuito impresso de quatro camadas são amplamente preferidas por sua compatibilidade eletromagnética (EMC) superior, integridade de energia e integridade de sinal.

Índice

PCB de 4 camadas Estrutura de empilhamento

O design da pilha é a base do desempenho de uma placa de 4 camadas. Uma pilha inadequada pode levar a interferência de sinal, ruído na fonte de alimentação e não conformidade com EMI.

1. Comparação entre esquemas clássicos de empilhamento

- Esquema 1 (recomendado)

- Camada superior: Camada de sinal

- Camada 2: Plano de aterramento (GND)

- Camada 3: Plano de alimentação (PWR)

- Camada inferior: Camada de sinal

- Vantagens: O plano de aterramento fornece uma referência sólida para os sinais da camada superior. Os planos de alimentação e aterramento adjacentes formam uma capacitância de desacoplamento inerente.

- Esquema 2

- Camada superior: Camada de sinal

- Camada 2: Plano de alimentação

- Camada 3: Plano de aterramento

- Camada inferior: Camada de sinal

- Cenários aplicáveis: Dispositivos de alta corrente (por exemplo, controladores de motor). Observe possíveis alterações no plano de referência para sinais da camada inferior.

- Esquema 3 (Usar com cuidado)

- Camada superior: Plano de aterramento

- Camada 2: Camada de sinal

- Camada 3: Camada de sinal

- Camada inferior: Plano de potência

- Riscos: Plano de terra incompleto, longos caminhos de retorno de sinal. Adequado principalmente para placas de baixa frequência, dominadas por conectores.

2. Configurações dos parâmetros principais

- Espessura dielétrica: Recommended 0.1–0.2mm between signal and reference planes to enhance inter-layer coupling.

- Peso do cobre: Outer layers 1oz (35μm), inner layers 0.5oz (17.5μm). Can increase to 2oz for high-current areas.

- Design Pullback: Power planes should be indented 40–80mil relative to the ground plane (20H rule) to reduce edge radiation.

Via Design

As vias são cruciais para as conexões entre camadas, mas introduzem parâmetros parasíticos que afetam os sinais de alta velocidade.

1. Por meio da seleção do tipo

- Vias de furo passante: Baixo custo, adequado para sinais padrão e conexões de energia.

- Vias cegas/enterradas: Usado para roteamento de escape BGA de alta densidade, mas aumenta o custo do processo.

2. Cálculo dos parâmetros parasitários

- Capacitância parasítica:

C ≈ 1.41ε · T · D1 / (D2 - D1)

OndeTé a espessura da placa,D1é o diâmetro da broca,D2é o diâmetro da almofada. - Indutância parasítica:

L ≈ 5.08h [ln(4h / d) + 1]

Ondehé através do comprimento,dé o diâmetro da broca.

3. Diretrizes de uso do Via

- Vias de energia: Use vias maiores (por exemplo, 12 mil de diâmetro/16 mil de perfuração), coloque várias em paralelo para reduzir a impedância.

- Vias de sinal: Prefira vias menores (por exemplo, 8 mil de diâmetro/12 mil de perfuração). Evite o posicionamento assimétrico em pares diferenciais.

- Vias térmicas: Coloque sob componentes geradores de calor (por exemplo, broca de 0,3 mm, passo de 1,5 mm).

Roteamento de PCB

1. Procedimento de encaminhamento

- Lide primeiro com as áreas difíceis: Comece o roteamento a partir de áreas complexas, como BGAs e interfaces de alta velocidade.

- Manuseio modular: Roteie por blocos funcionais (por exemplo, MCU, memória, circuitos analógicos) para evitar interferência cruzada.

- Roteamento de limpeza: Encaminhe os sinais de baixa velocidade por último, otimizando a utilização do canal através do ajuste da largura e do espaçamento do traço.

2. Regras críticas de roteamento

- Controle de impedância:

- Single-ended: 50Ω. Differential pairs: 100Ω.

- Consiga ajustando a largura do traço, a espessura dielétrica e a permissividade.

- Manipulação de sinais de alta velocidade:

- Priorize o roteamento de sinais de clock nas camadas internas, com referência a um plano de aterramento.

- Maintain length matching in differential pairs (≤5mil tolerance).

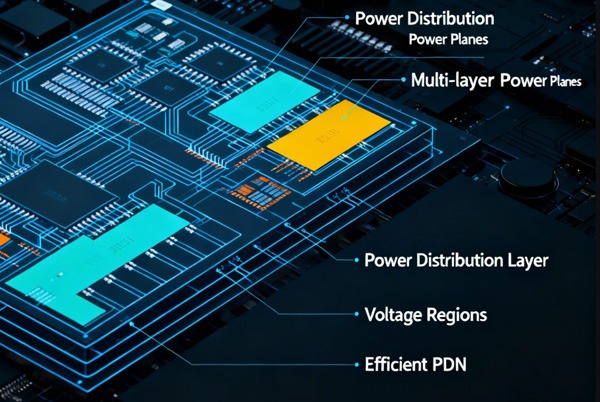

- Segmentação do plano de potência:

- Segmente um único plano de alimentação em no máximo 3 regiões (por exemplo, 3,3 V, 5 V, 12 V).

- Use segmentation lines ≥0.5mm wide to prevent creepage issues.

Projeto de integridade de energia

1. Posicionamento do capacitor de desacoplamento

- Seleção: 0.1μF ceramic capacitors (high-frequency) + 10μF tantalum capacitors (low-frequency).

- Colocação: Position close to IC power pins (≤3mm). Connect directly to power/ground planes via vias.

2. Integridade do plano de aterramento

- Evite dividir o plano de aterramento com traços de sinal para garantir caminhos de retorno de baixa impedância.

- Connect digital and analog grounds at a single point using a ferrite bead or 0Ω resistor.

Verificação do projeto e preparação da produção

1. Lista de verificação da RDC

- Trace Width/Spacing: General signals ≥6/6mil, Power traces ≥12/12mil.

- Drill-to-Copper Distance: ≥8mil to prevent short circuits.

2. Simulação da integridade do sinal

- Use ferramentas como HyperLynx ou Sigrity para verificar o tempo de subida, o ringing e a continuidade da impedância.

- Concentre-se em verificar relógios, sinais diferenciais e ondulação da fonte de alimentação.

3. Saída do arquivo de produção

- Forneça arquivos Gerber (incluindo camadas, máscara de solda, perfuração), cupons de teste de impedância e desenhos de montagem.

Principais conclusões sobre o design

- Esquema de empilhamento preferencial 1, garantindo um plano de aterramento adjacente às camadas de sinal primárias.

- Equilibre custo e desempenho por meio do design, utilizando vias de alimentação paralelas para reduzir a impedância.

- Rota seguindo o princípio “Difícil Primeiro”, priorizando sinais de alta velocidade nas camadas internas.

- Limitar a segmentação de energia a 3 regiões, colocando capacitores de desacoplamento próximos aos ICs.

- Valide com DRC e simulação para evitar retrabalho na pós-produção.